基本流程:①设计定义 ②设计输入 ③分析综合 ④功能仿真 ⑤布局布线 ⑥分析性能

1.启动软件

双击 Vivado图标即可启动 Vivado 软件。

2.创建工程

①Quick Start 组包含有 Create Project(创建工程) Open Project(打开工程)OpenExample Project(打开实例工程)。

②Tasks 组包含有 Manage IP(管理 IP) Open Hardware Manager (打开硬件管理器)Xilinx Tcl Store(Tcl 脚本存储库)。

③Learning Center 组包含有 Documentation and Tutorials(文档和教程) QuickTakeVideos(快速上手视频) Release Notes Guide(发布注释向导)。

通过单击 Quick Start 组的 Create Project 来新建一个 Vivado 设计工程。

进入到 Project Name 对话框后,填入工程名称以及工程路径, 根据实际情况确定是否勾选复选框 Create project subdirectory,由于默认勾选了该选项, Vivado 会在所选工程目录下自动创建一个与工程名同名的文件夹,用于存放工程内的各种文件。并且 Vivado 会自动管理工程文件夹内的各种工程文件,并创建相应的子目录,这为我们的开发工作带来了很大的便捷。此处我们需要注意的是,工程路径与工程名一定不能包含空格以及中文字符,否则在后续流程中会出现错误。然后单击 Next 按钮。

出现 Project Type 对话框,如图所示。 Vivado 工具可以创建多种不同类型的工程,如最常使用的 RTL 工程、综合后的网表工程、 IO 规划工程以及导入其他设计工具的工程。在这里我们选择 RTL 类型的工程,我们可以在创建工程的阶段进行设计文件的添加或创建,也可以在工程创建完成后再进行设计文件的添加或创建。此处我们勾选下面的复选框 Do not specify sources at this time,不在设计创建阶段进行添加源文件。单击 Next 按钮。

在这个我们需要选择设计所用的具体 FPGA芯片的型号,根据板卡所用 FPGA 的器件系列、封装、速度等级以及温度级别来进行筛选,如图所示。选择完成后单击 Next 按钮。之后点击Finish完成创建。

3.添加源文件

在 Flow Navigator 下,找到 Project Manager 并展开,单击 Project Manager 下的 Add Sources 选项;或者在 Sources 面板下单击 按钮,面板如图所示。

1) Add or Create Constraints(添加或者创建约束);

2) Add or Create Design Sources(添加或者创建设计源文件);

3) Add or Create Simulation Sources(添加或者创建仿真文件);

点击Float可以悬浮窗口:

我们简单写一个二选一多路器的代码:

module themux2(

a,

b,

sel,

out

);

input a;

input b;

input sel;

output out;

//二选一多路器

assign out = (sel==1)?a:b;

endmodule

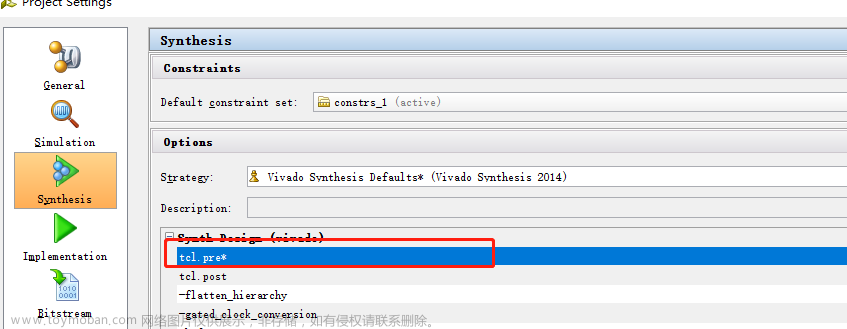

4.设计综合

点击快捷键进行操作:

综合时右上角会有一个绿色圆圈在转,完成后我们可以看一下报告,没有红色也就是没有语法错误和逻辑错误。

5.仿真

下面是二选一多路器的testbench:

`timescale 1ns/1ns

module themux2_tb();文章来源:https://www.toymoban.com/news/detail-626614.html

reg s_a;

reg s_b;

reg sel;

wire out;

themux2 themux2(//后面是例化名称

.a(s_a),

.b(s_b),

.sel(sel),

.out(out)

);

initial begin

s_a = 0;s_b = 0; sel = 0;

#200;

s_a = 0;s_b = 0; sel = 1;

#200;

s_a = 0;s_b = 1; sel = 0;

#200;

s_a = 0;s_b = 1; sel = 1;

#200;

s_a = 1;s_b = 0; sel = 0;

#200;

s_a = 1;s_b = 0; sel =1;

#200;

s_a = 1;s_b = 1; sel = 0;

#200;

s_a = 1;s_b = 1; sel = 1;

#200;

end

endmodule文章来源地址https://www.toymoban.com/news/detail-626614.html

到了这里,关于【FPGA】Vivado开发流程(基于2018.3版本)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!