always语句块一定条件写完整,否则电平触发,综合生成锁存器

task不可综合,主要用于仿真/验证

大部分都是并行执行的,只有begin end块中阻塞语句是串行文章来源:https://www.toymoban.com/news/detail-628798.html

if-else和case的区别

if-else面积小,但时延(执行时间)大

case面积大,但delay小(会被转换为查找表lookup table)文章来源地址https://www.toymoban.com/news/detail-628798.html

到了这里,关于Verilog学习记录-自用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

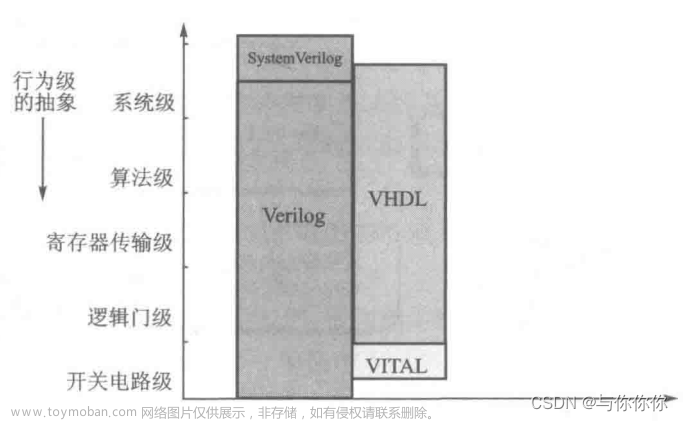

![[蔡觉平老师主讲] Verilog HDL数字集成电路设计原理与应用](https://imgs.yssmx.com/Uploads/2024/04/848792-1.png)