1 测试工程

使用QDMA的Example工程,该工程可从Github下载,使用的FPGA板卡为浪潮的F37X加速器,运行工程目录下的run.sh执行run.tcl即可完成工程的创建和编译。

2 驱动安装

本节主要介绍QDMA驱动的源文件、编译和安装过程。

2.1 源文件说明

1.下载地址:DMA驱动下载

2.文件说明

| 文件 | 说明 |

|---|---|

| apps | 应用文件 |

| docs | 说明文件 |

| driver | 驱动源文件 |

| scripts | 脚本文件 |

| RELEASE | 版本说明 |

| Makefile.txt | Makefile |

| bsd_license.txt | 证书 |

| COPYING | 权限 |

| license.txt | 证书 |

2.2 驱动编译安装

1.依赖库安装:QDMA驱动依赖于libaio,所以在编译驱动前需要安装该库。

sudo apt-get install libaio-dev

2.驱动编译

2.1 执行make clean && make命令完成驱动文件的编译,在文件夹会生成bin文件夹,里面包含下述文件。如果需要添加新设备,可以在driver/src/pci_ids.h文件中添加。

| 文件 | 说明 |

|---|---|

| dma-ctl | QDMA的控制和配置应用程序 |

| dma-to-device | 执行MM或ST模式的host-to-card的传输事务 |

| dma-from-device | 执行MM或ST模式的card-to-host的传输事务 |

| dma-perf | 测量QDMA的性能 |

| qdma-pf.ko | PF驱动 |

| qdma-vf.ko | VF驱动 |

| dma-latency | 测量ST H2C/C2H传输的乒乓延时 |

| dma-xfer | 说明QDMA传输的简单应用 |

2.2 如果只需要PF驱动可以执行make driver MODULE=mod_pf

2.3 如果只需要VF驱动可以执行make driver MODULE=mod_vf

2.4 如果要启用CPM5的VF 4K队列,执行make EQDMA_CPM5_VF_GT_256Q_SUPPORTED=1

3.驱动安装

3.1 执行sudo make install安装驱动和应用程序,执行完该命令后在/user/local/sbin文件下生成dma-ctl、dma-to-device等应用程序,在/lib/modules/<kernel version>/qdma文件夹下生成qdam-pf.ko和qdma-vf.ko驱动程序。

3.2 如果只安装驱动程序,可以执行sudo make install-mods

3.3 如果只安装应用程序,可以执行sudo make install-apps

3.4 如果需要卸载驱动和应用程序,可以执行sudo make uninstall

4.驱动加载

4.1 下载FPGA程序,执行lspci -vd <vendor id>找到设备的BDF号。

4.2 在加载驱动前需要生成一个qdma.conf文件放到/etc/modprobe.d文件夹下,用于参数传递。在scripts文件夹下有一个qdma_generate_conf_file.sh脚本,辅助生成配置文件。执行下述命令,脚本会自动在/etc/modprobe.d文件夹下生成qdma.conf文件。

sudo ./qdma_generate_conf_file.sh <bus_num> <num_pfs> <mod> <config_bar> <master_pf>

| 参数 | 说明 |

|---|---|

| bus_num | BDF中的B |

| num_pfs | PF支持的数量,默认为4 |

| mod | 驱动的模式,默认为0 0-Auto;1-Poll;2-Direct Interrupt 3-Indirect Interrupt; 4-Legacy Interrupt |

| config_bar | 配置的BAR空间 |

| master_pf | 主PF |

4.3 执行sudo modprobe qdma-pf加载PF驱动,执行sudo modprobe qdma-vf加载VF驱动。由于在/lib/modules/<kernel version>/qdma文件夹下有qdam-pf.ko和qdma-vf.ko驱动程序,所以系统在启动时会自动加载这两个驱动。如果不需要开机加载这两个驱动,可以在/etc/modprobe.d/blacklist.cof文件中添加blacklist qdma-pf和blacklist qdma-vf语句。

5.修改qmax

执行下述命令修改最大队列数,安装驱动后默认的qmax是0,在执行测试脚本时出现错误,提示“unable to open device /dev/qdma82000-MM-0”。重启系统后这个值会恢复为0。

cat /sys/bus/pci/devices/0000:01:00.0/qdma/qmax // 显示qmax

echo 8 > /sys/bus/pci/devices/0000:01:00.0/qdma/qmax // 设置qmax为8

6.设置VF数量

cat /sys/bus/pci/devices/0000:01:00.0/sriov_totalvfs // 显示每个PF的VF数量

echo 3 > /sys/bus/pci/devices/0000:01:00.0/sriov_numvfs // 设置每个PF的VF数量为1024

3 调试工具

3.1 设备管理

应用dma-ctl用于管理驱动,可以实现下述功能,通过命令dma-ctl -h可查看帮助文件。

- 列出设备信息

dma-ctl dev list // 列出系统可使用的PF和VF,以及每个function的queue base和queue max

dma-ctl qdma<bdf> cap // 列出硬件和软件的版本信息

dma-ctl qdma<bdf> stat // 列出数据统计信息

- 添加一个或多个队列

dma-ctl qdma<bdf> q add idx <N> [mode <st|mm>] [dir <h2c|c2h|bi|cmpt>] // N-队列编号

dma-ctl qdma<bdf> q add list <start_idx> <num_Qs> [mode <st|mm>] [dir <h2c|c2h|bi|cmpt>]

- 开始一个或多个队列

dma-ctl qdma<bdf> q start idx <N> [dir <h2c|c2h|bi|cmpt>]

dma-ctl qdma<bdf> q start list <start_idx> <num_Qs> [dir <h2c|c2h|bi|cmpt>]

- 暂停一个或多个队列

dma-ctl qdma<bdf> q stop idx <N> [dir <h2c|c2h|bi|cmpt>]

dma-ctl qdma<bdf> q stop list <start_idx> <num_Qs> [dir <h2c|c2h|bi|cmpt>]

- 删除一个或多个队列

dma-ctl qdma<bdf> q del idx <N> [dir <h2c|c2h|bi|cmpt>]

dma-ctl qdma<bdf> q del list <start_idx> <num_Qs> [dir <h2c|c2h|bi|cmpt>]

- 输出一个或多个队列信息

dma-ctl qdma<bdf> q dump idx <N> [dir <h2c|c2h|bi|cmpt>]

dma-ctl qdma<bdf> q dump list <start_idx> <num_Qs> [dir <h2c|c2h|bi|cmpt>]

- 输出一个或多个队列描述符信息

dma-ctl qdma<bdf> q dump idx <N> [dir <h2c|c2h|bi|cmpt>] [desc <x> <y>] // <x>-range start;<y>-range end

dma-ctl qdma<bdf> q dump list <start_idx> <num_Qs> [dir <h2c|c2h|bi|cmpt>] [desc <x> <y>]

- 输出一个或多个队列完成信息

dma-ctl qdma<bdf> q dump idx <N> [dir <h2c|c2h|bi|cmpt>] [cmpt <x> <y>]

dma-ctl qdma<bdf> q dump list <start_idx> <num_Qs> [dir <h2c|c2h|bi|cmpt>] [cmpt <x> <y>]

输出中断信息

dma-ctl qdma<bdf> intring dump vector <N> <start_idx> <end_idx>

3.2 数据读写

- 读寄存器

dmactl qdma<bdf> reg read bar <N> <addr> // N-Bar号;addr-地址

- 写寄存器

dmactl qdma<bdf> reg write bar <N> <addr>

- 输出队列寄存器

dmactl qdma<bdf> reg dump [dmap <Q> <N>] // Q-队列号;N-队列数量

- 写入数据

dma-to-device [OPTIONS]

-d (--device) device path from /dev. Device name is formed as qdmabbddf-<mode>-<queue_number>

-a (--address) the start address on the AXI bus

-s (--size) size of a single transfer in bytes, default 32 bytes

-o (--offset) page offset of transfer

-c (--count) number of transfers, default 1

-f (--data input file) filename to read the data from.

-w (--data output file) filename to write the data of the transfers

-h (--help) print usage help and exit

-v (--verbose) verbose outpu

- 读出数据

dma-from-device [OPTIONS]

-d (--device) device path from /dev. Device name is formed as qdmabbddf-<mode>-<queue_number>

-a (--address) the start address on the AXI bus

-s (--size) size of a single transfer in bytes, default 32 bytes.

-o (--offset) page offset of transfer

-c (--count) number of transfers, default is 1.

-f (--file) file to write the data of the transfers

-h (--help) print usage help and exit

-v (--verbose) verbose output

4 测试分析

4.1 测试脚本

执行脚本qdma_run_test_pf.sh完成对PF的测试,执行命令如下,整个测试流程包括获取设备、设置复位、h2c和c2h的mm接口测试、h2c的st接口测试和c2h的st接口测试。

sudo ./qdma_run_test_pf.sh <bdf> <qid_start> <num_qs> <desc_bypass_en> <pfetch_en> <pfetch_bypass_en> <flr_on>

| 参数 | 说明 |

|---|---|

| bdf | 设备的BDF号 |

| qid_start | 队列的起始ID |

| num_qs | 从qid_start开始的队列数量,默认为04 |

| desc_bypass_en | 使能描述符旁路,默认为0 |

| pfetch_en | 使能预取,默认为0 |

| pfetch_bypass_en | 使能预取旁路,默认为0 |

| flr_on | 启用function level reset,默认为0 |

- 获取设备:get_dev

执行dma-ctl dev list获取设备信息。 - 设置复位:set_flr

如果设置了function level reset,则对修改系统中的reset文件对PCIe设备进行复位。 - MM测试:run_mm_h2c_c2h

1.找到AXI Lite的bar空间:get_user_bar

2.设置设备:dev_mm_c2h、dev_mm_h2c、out_mm

3.开始队列传输:queue_start,执行dma-ctl q add、dma-ctl q start

4.传输数据到FPGA:dma_to_device

5.从FPGA中取出数据:dma_from_device

6.比较两个文件的内容是否相等,结束测试。

7.清理队列:cleanup_queue,执行dma-ctl q stop、dma-ctl q del - H2C测试

1.找到AXI Lite的bar空间:get_user_bar

2.设置设备:dev_st_h2c

3.开始队列传输:queue_start,执行dma-ctl q add、dma-ctl q start

4.传输数据到FPGA:dma_to_device

5.读取FPGA的数据对比结果dma-ctl reg read,结束测试。

6.清理队列:cleanup_queue,执行dma-ctl q add、dma-ctl q start - C2H测试

1.找到AXI Lite的bar空间:get_user_bar

2.设置设备:dev_st_c2h、out_st

3.开始队列传输:queue_start,执行dma-ctl q add、dma-ctl q start

4.传输数据到FPGA:dma_from_device

5.比较两个文件的内容是否相等,结束测试。

6.清理队列:cleanup_queue,执行dma-ctl q add、dma-ctl q start

4.2 测试结果

- 查看PCIe设备

- 查看驱动加载情况

- 查看驱动绑定的设备信息, 如果qmax为0,则需要设置非零的qmax,否则无法找到设备。

- 测试结果

test_mm)

dma-ctl qdma82000 q add idx 0 mode mm dir bi

dma-ctl qdma82000 q start idx 0 dir bi

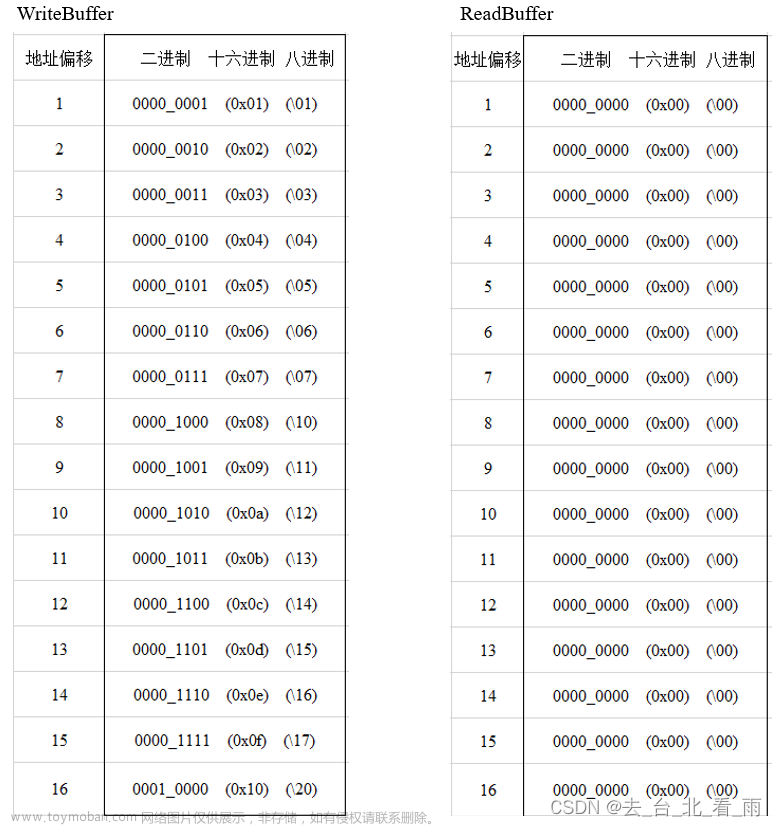

dma-to-device -d /dev/qdma82000-MM-0 -f datafile_16bit_pattern.bin -s 1024

dma-from-device -d /dev/qdma82000-MM-0 -f /tmp/out_mm82000_0 -s 1024

cmp /tmp/out_mm82000_0 datafile_16bit_pattern.bin -n 1024

dma-ctl qdma82000 q stop idx 0 dir bi

dma-ctl qdma82000 q del idx 0 dir bi

;;

test_st_h2c)

dma-ctl qdma82000 q add idx 0 mode st dir bi

dma-ctl qdma82000 q start idx 0 dir bi

dma-ctl qdma82000 reg write bar 2 0x0C 0x1

dma-to-device -d /dev/qdma82000-ST-0 -f datafile_16bit_pattern.bin -s 1024

dma-ctl qdma82000 reg read bar 2 0x10

dma-ctl qdma82000 q stop idx 0 dir bi

dma-ctl qdma82000 q del idx 0 dir bi

;;

文章来源:https://www.toymoban.com/news/detail-631911.html

文章来源:https://www.toymoban.com/news/detail-631911.html

test_st_c2h)

dma-ctl qdma82000 reg write bar 2 0x0 0x0

dma-ctl qdma82000 q add idx 0 mode st dir bi

dma-ctl qdma82000 q start idx 0 dir bi

dma-ctl qdma82000 reg write bar 2 0x4 1024

dma-ctl qdma82000 reg write bar 2 0x08 2

dma-from-device -d /dev/qdma82000-ST-0 -f /tmp/out_st82000_0 -s 1024

cmp /tmp/out_st82000_0 datafile_16bit_pattern.bin -n 1024

dma-ctl qdma82000 reg write bar 2 0x08 0x22

dma-ctl qdma82000 q stop idx 0 dir bi

dma-ctl qdma82000 q del idx 0 dir bi

;;

文章来源地址https://www.toymoban.com/news/detail-631911.html

文章来源地址https://www.toymoban.com/news/detail-631911.html

到了这里,关于Xilinx QDMA说明和测试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!