实现高速数据采集的FPGA系统设计

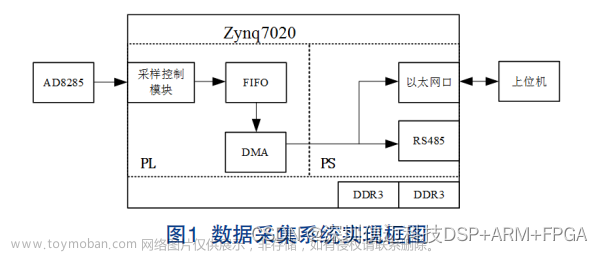

高速数据采集是现代通信、测量等领域中的重要应用,需要对海量数据进行快速且准确的采集。基于FPGA的高速数据采集系统是一种有效的实现方案,因为FPGA可以灵活且高效地处理大规模数据并实现高速串行数据输入输出。本文将介绍一个基于FPGA的高速数据采集系统,该系统可实现高速数据采集和数据传输。

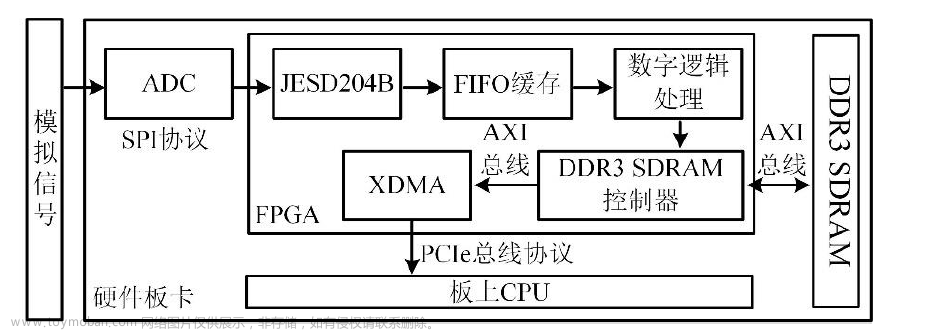

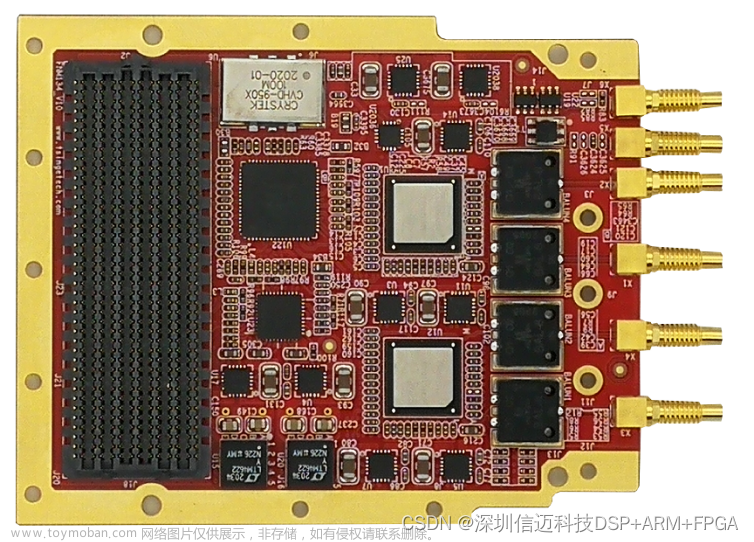

首先,我们需要确定FPGA芯片型号和开发工具。在本系统中,我们选择了Xilinx公司的Kintex UltraScale FPGA,并使用Vivado开发套件进行开发。接下来,我们需要设计数据采集模块和数据传输模块。文章来源:https://www.toymoban.com/news/detail-632012.html

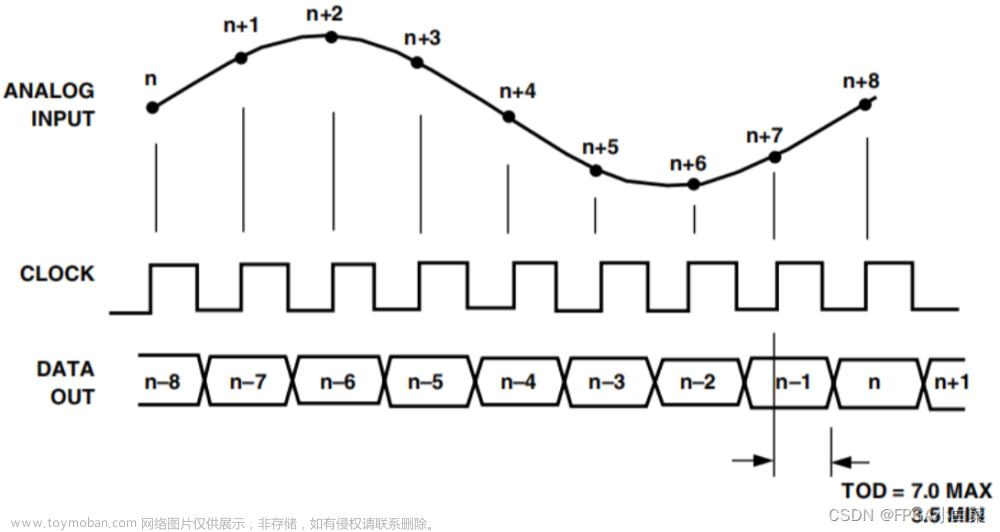

数据采集模块的设计需要考虑到数据采集速度和硬件资源的使用效率。在本系统中,我们使用了多通道ADC芯片(例如AD7616),并通过SPI总线控制实现对该芯片的数据采集。具体实现如下:文章来源地址https://www.toymoban.com/news/detail-632012.html

module adc_controller

(

input wire clk, // 时钟信号

input wire rst, // 复位信号

input wire [7:0] adc_cmd, // ADC芯片的命令

output reg [15:0] adc_data // ADC芯片采集到的数据

);

reg [15:0] spi_out; // SPI总线输出

reg [7:0] spi_in; // SPI总线输入

reg [7:0] cmd_cnt;

reg [7:0] bit_cnt;

reg [3:0] state;

assign adc_data = spi_in[7:0];

// 状态机

always @ (posedge clk or posedge rst)

begin

if (rst) begin

state <= 0;

spi_out <= 16'h0000;

spi_in <= 8'h00;

cmd_cnt <=到了这里,关于实现高速数据采集的FPGA系统设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!