简介

在图像处理领域中,降采样是一个非常常用的图像处理方法,目的是为了在大体上不改变图片的情况下,缩小图像,降低分辨率,减少数据的计算量,生成对应图像的降采样图。本质就是抽取图像数据来降低特征的维度进而保留有效的信息。

原理

对一个需要处理的图片的像素值序列间隔几个像素值取样一次,也就是抽取像素值,得到的新的像素值序列就是原像素值序列的降采样,也称为下采样。

降采样分为整数倍降采样和分数倍降采样,在这篇文章中,介绍的是比较常用的 2 倍降采样,也可以说是奇数降采样或偶数降采样。

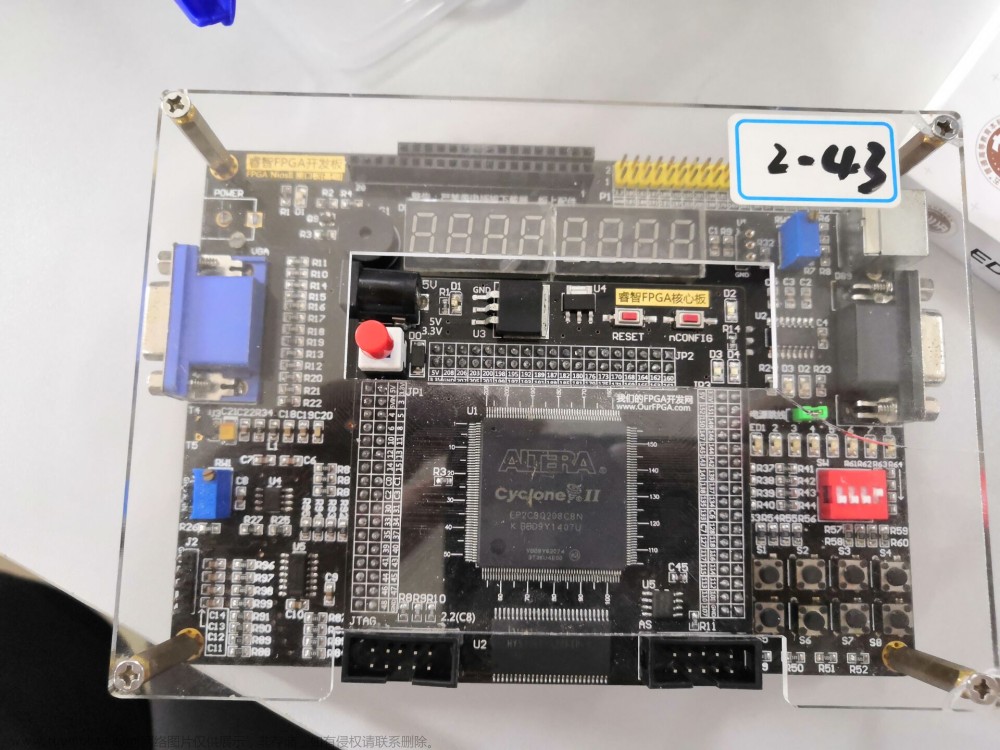

模块端口图

这里把 RGB 数据的三个通道都列了出来,当然也可以用其他的图像数据格式,如:YUV 。

设计文件代码

以下为降采样的设计代码,留下的是偶数列的图像数据。代码中控制计数器的为 MCNT,也就是计数最大值,这个视情况而定,也可用数据有效信号(Data_valid)来控制计数器。 文章来源:https://www.toymoban.com/news/detail-633171.html

module Down_Sampling(

Data_in_r,

Data_in_g,

Data_in_b,

clk,

rst_n,

Data_out_r,

Data_out_g,

Data_out_b,

);

input [7:0] Data_in_r;

input [7:0] Data_in_g;

input [7:0] Data_in_b;

input clk;

input rst_n;

output [7:0] Data_out_r;

output [7:0] Data_out_g;

output [7:0] Data_out_b;

parameter MCNT = 根据情况定 也可用数据有效信号控制;

reg [10:0] Data_cnt;

always@(posedge clk or negedge rst_n)

if(!rst_n)

Data_cnt <= 0;

else if(Data_cnt == MCNT)

Data_cnt <= 0;

else

Data_cnt <= Data_cnt + 1;

always@(posedge clk or negedge rst_n)

if(!rst_n)begin

Data_out_r <= 0;

Data_out_g <= 0;

Data_out_b <= 0;

end

else if(!Data_cnt[0])begin

Data_out_r <= Data_in_r;

Data_out_g <= Data_in_g;

Data_out_b <= Data_in_b;

end

else begin

Data_out_r <= Data_out_r;

Data_out_g <= Data_out_g;

Data_out_b <= Data_out_b;

end

endmodule以下为留下奇数列的图像数据。文章来源地址https://www.toymoban.com/news/detail-633171.html

module Down_Sampling(

Data_in_r,

Data_in_g,

Data_in_b,

clk,

rst_n,

Data_out_r,

Data_out_g,

Data_out_b,

);

input [7:0] Data_in_r;

input [7:0] Data_in_g;

input [7:0] Data_in_b;

input clk;

input rst_n;

output [7:0] Data_out_r;

output [7:0] Data_out_g;

output [7:0] Data_out_b;

parameter MCNT = 根据情况定 也可用数据有效信号控制;

reg [10:0] Data_cnt;

always@(posedge clk or negedge rst_n)

if(!rst_n)

Data_cnt <= 0;

else if(Data_cnt == MCNT)

Data_cnt <= 0;

else

Data_cnt <= Data_cnt + 1;

always@(posedge clk or negedge rst_n)

if(!rst_n)begin

Data_out_r <= 0;

Data_out_g <= 0;

Data_out_b <= 0;

end

else if(Data_cnt[0])begin

Data_out_r <= Data_in_r;

Data_out_g <= Data_in_g;

Data_out_b <= Data_in_b;

end

else begin

Data_out_r <= Data_out_r;

Data_out_g <= Data_out_g;

Data_out_b <= Data_out_b;

end

endmodule到了这里,关于Down-Sampling 降采样(Verilog)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!