扰码模块的目的之一是可以避免频谱尖峰,另一个目的是可使频谱数据独立,使电气接口的频谱选择更有效,避免数据错误。然而,扰码模块的使用会使转换器中所有数字模块会产生一些转换噪声。所以,JESD204B 标准的一些模式不使用扰码模式。

【JESD204系列】六、加解扰模块的设计原理

从传输层输出的用户数据会进入到加扰层,加扰层的主要目的是对传输数据进行扰码,由于传输数据可能具有一定的周期性,该周期性导致了传输数据频谱在某一频点处出现峰值,对后续的模拟处理及传输带来了一定困难,为了随机化传输数据,让传输的数据看起来更像“噪声”,在发送端和接收端分别引入了加扰电路和解扰电路。

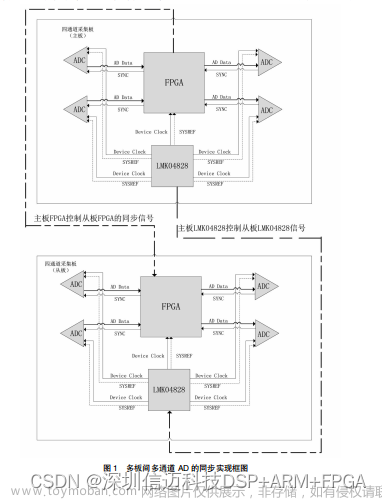

加解扰电路通常由移位寄存器和异或门实现,其阶数由扰码多项式决定,JESD204B 协议规定扰码多项式为1+X14+X15。加解扰是逐帧发送数据和接收数据的,每个通道每帧数据都需要被加扰和解扰,如图1为逐帧加扰/解扰数据示意图。

从图1中可以看到,数据传输是以帧为单位的,输入的帧数据流Input framestream,如Frame0、Frame1、Frame2 等,经过加扰/解扰模块,逐帧进行加解扰,然后将扰码后的数据逐帧进行输出,构成输出的帧数据流Output frame stream。

JESD204B 协议规定加解扰电路采用自同步扰码方式,且扰码为可选项,传输数据既可扰码亦可不扰码。串行自同步加扰与解扰电路结构如图2所示。

图2 中Dn 为加扰电路输入数据以及解扰电路输出数据,Sn 为加扰输出和解扰输入数据,S0~S14 为15 阶移位寄存器扰码种子,加扰电路中S1 和S0 异或之后再和输入数据Dn 异或得到扰码输出Sn,同时Sn 移入寄存器更新为扰码种子。扰码分为串行扰码和并行扰码。串行加扰公式很容易推导得到,为 Sn =Dn⊕Sn-14⊕Sn-15 ,式中⊕ 号为模二加。串行扰码中移位寄存器中的扰码种子每周期移动1 位,但是这样扰码效率很低,故一般采用并行扰码。 以8位并行扰码为例,移位寄存器每周期移动8位。

由串行加扰公式推导出的8位并行加扰公式如下式所示:

解扰公式为:

由于协议规定加扰器位于传输层和数据链路层之间,而数据从传输层发送到链路层进行传输时,要通过代码组同步(CGS)和初始通道对齐序列(ILAS)两个步骤,根据协议规定,该两个步骤的数据均不能加扰。并且为了实现接收端解扰器的自同步,需要将加扰器的初始寄存器数据配置作为两个未加扰的字节进行发送,这样接收端的解扰器在收到初始寄存器配置数据后,根据该数据对解扰器的寄存器进行配置,从而实现正确解扰的功能。出于以上两个原因,需要在加扰/解扰模块中添加一个使能信号,以便对加扰过程进行灵活的控制,从而实现功能要求。

下图3为添加了使能信号后的加扰/解扰模块框图。

由图中可以看出,在输入异或之前添加一个与,从而实现当使能信号为0 时,发送端不进行加扰,接收端也不进行解扰;反之当使能信号为1 时,发送端进行加扰,接收端进行解扰。可以用以下公式描述:

如前文所述,传输层将数据映射为以8 位字节为基础的数据格式,因此为了方便处理,相应的加扰模块的数据宽度通常也为8 的倍数,即8 位、16 位、32 位等位宽的加扰/解扰模块。因此在串行加扰模块的原理基础上,进行多位并行的加扰/解扰模块设计。并行加扰/解扰模块逻辑框图如下图4和图5 所示。

在基本的串行加扰电路中,一个时钟周期进行一次运算,在时钟周期结束时将当前输出移入移位寄存器,因此处理8 位数据的加扰就需要8个时钟周期,并且移位寄存器的值要移动八位。也就是说,当第一个输入是与S0和S1的异或结果进行异或,从而得到输出,并且将此输出移入循环寄存器,此时的S0和S1即为上一个时钟周期的S1和S2,也就是说S = S0 + S1 + D = S′1 + S′2 + D,其中S′1和S′2代表上个周期的S1和S2,从而我们可以用第一个周期中已知的参数将第二个周期的加扰算法表示出来。以此类推,八个周期处理的八位数据都可以通过已知的参数表示,从而在一个周期内进行运算,也就是8 位并行加扰/解扰模块的原理, 具体公式为:

再添加使能控制信号之后,即可实现带有使能控制功能的8bit 并行加解扰模块。文章来源:https://www.toymoban.com/news/detail-635015.html

文章来源地址https://www.toymoban.com/news/detail-635015.html

文章来源地址https://www.toymoban.com/news/detail-635015.html

到了这里,关于【JESD204系列】六、加解扰模块的设计原理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!