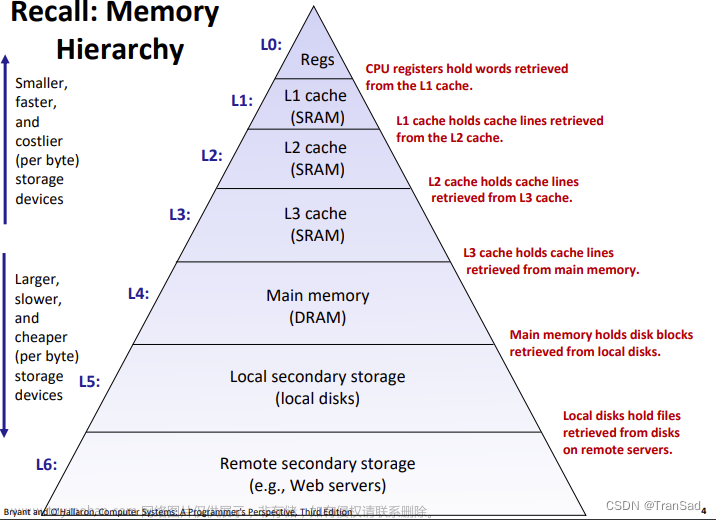

分级说明

-

L1缓存的标准延迟是4个周期。这意味着,当CPU请求数据时,L1缓存需要4个时钟周期来将数据传输给CPU。

-

L2缓存的标准延迟是12个周期。相对于L1缓存,L2缓存的容量更大,但其读取速度更慢,需要更多的时钟周期来传输数据。

-

L3缓存的标准延迟是43个周期。与L2缓存相比,L3缓存的容量更大,但其读取速度更慢,需要更多的时钟周期来传输数据。

-

RAM的标准延迟是62个周期加上100纳秒。RAM是计算机系统中最慢的存储层级之一,读取数据需要更多的时钟周期和更长的时间。

作用说明

当数据被访问时,计算机系统中的不同存储层级(缓存和RAM)扮演着不同的角色和速度。以下是对每个存储层级的详细说明:

- L1缓存:L1缓存是位于CPU内部的第一级缓存。它有较小的容量,但读取速度非常快。L1缓存存储着最常用的数据和指令,以便CPU可以快速访问它们。标准延迟为4个周期,这意味着当CPU请求数据时,L1缓存需要4个时钟周期来将数据传输给CPU。

- L2缓存:L2缓存是位于CPU和RAM之间的第二级高速缓存。相比于L1缓存,L2缓存容量更大,但读取速度要慢一些。它也存储着常用的数据和指令,以备CPU需要时快速访问。标准延迟为12个周期,这意味着当CPU请求数据时,L2缓存需要12个时钟周期来将数据传输给CPU。

- L3缓存:L3缓存是位于CPU和RAM之间的第三级高速缓存。相对于L2缓存,L3缓存的容量更大,但读取速度更慢。它起到了更大规模的数据存储的作用,以供CPU在需要时快速访问。标准延迟为43个周期,这意味着当CPU请求数据时,L3缓存需要43个时钟周期来将数据传输给CPU。

- RAM:RAM(随机访问内存)是计算机系统中的主要存储器,用于存储大量的数据和程序。RAM容量较大,但读取速度最慢。标准延迟为62个周期加上100纳秒,这意味着当CPU请求数据时,RAM需要62个时钟周期加上100纳秒的时间来将数据传输给CPU。

存储分级设计思想

在计算机系统设计中,存储层级的选择和使用是一个关键的设计问题,它旨在平衡存储器容量、访问速度和成本之间的关系。以下是一些常见的设计关键点和设计思想:文章来源:https://www.toymoban.com/news/detail-637301.html

- 局部性原理(Locality Principle):计算机程序中的数据和指令往往表现出一定的局部性。这意味着在一段时间内,CPU更有可能访问最近访问过的数据。因此,在设计存储层级时,需要将频繁访问的数据放置在速度更快的缓存层级中,以提高访问速度。

- 容量-延迟平衡(Capacity-Latency tradeoff):缓存的容量越大,可以存储的数据越多,但读取速度相对较慢。相反,容量较小的缓存读取速度较快,但能够存储的数据量有限。设计者需要根据系统的需求和成本考虑,综合考虑容量和延迟之间的平衡。

- 多级缓存层次(Multi-level caching):为了提供更高的性能,许多计算机系统不仅具有单个缓存层级,而是采用多级缓存层次结构。较小且更接近CPU的层级(如L1缓存)用于存储最频繁访问的数据,而较大且更接近RAM的层级(如L2和L3缓存)用于存储较少访问但仍然重要的数据。这样的多级缓存层次可以提供更好的容量-延迟平衡和性能潜力。

- 缓存替换策略(Cache replacement policies):由于缓存的容量是有限的,当缓存满时,需要根据一定的策略来决定替换哪些数据。常见的缓存替换算法包括最近最少使用算法(Least Recently Used,LRU)、最不经常使用算法(Least Frequently Used,LFU)等。选择合适的替换策略可以最大限度地提高缓存的命中率。

- 高速缓存一致性(Cache coherence):在多处理器系统中,每个处理器都有自己的缓存。为了保持数据的一致性,需要采取一些机制来确保各个缓存之间的数据一致。常见的高速缓存一致性协议包括MSI(Modified, Shared, Invalid)和MESI(Modified, Exclusive, Shared, Invalid)等。

通过合理地选择存储层级、优化缓存容量和延迟的平衡、设计高效的缓存替换策略和实现高速缓存一致性,可以提高计算机系统的性能和效率。这些设计关键点和设计思想在计算机体系结构中扮演着重要的角色。文章来源地址https://www.toymoban.com/news/detail-637301.html

到了这里,关于计算机体系中的不同的缓存存储层级说明的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!