站在一个IC前端设计人员的角度学习DFT基础知识,概念。

· 验证和测试的区别。

验证主要是确认功能,时序是否满足要求,一般在仿真环境中,输入激励,分析响应。根据验证阶段可以分为功能仿真,门级仿真,版图后仿真。

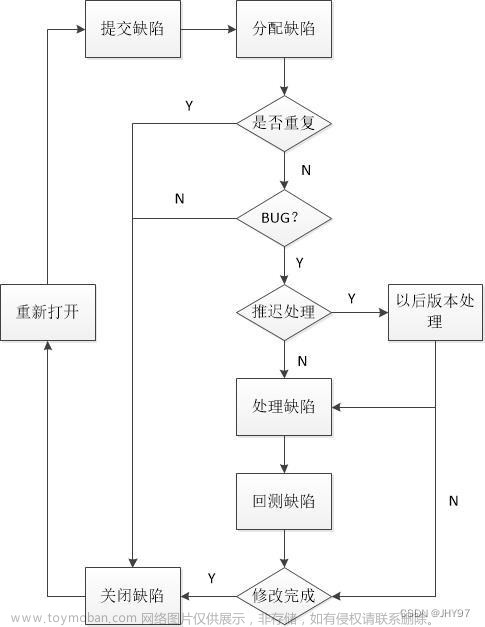

然而在芯片制造过程中,受到各种不确定因素的影响,制造出来的芯片并不完全都能正常工作,检测出有制造缺陷的芯片就是测试的范畴。测试要检查的不是设计的功能错误,而是芯片生产过程中引入的电路结构上的制造缺陷。对测试工程师来说,一块芯片的功能,用途都不重要,那些实在设计阶段由前端设计人员保证的内容。

为什么需要DFT。(Design For Test)

因为芯片设计规模越来越大,测试成本不断提高,封装后的芯片还要经过ATE(Auto Test Equipment)自动测试机台的检查后,才能够确保芯片质量,交付客户。测试机台的测试激励如果人为设定的话,很难保证故障覆盖率。为了方便测试激励的生成,在设计阶段就有意识的加入一定用于测试的附加逻辑,从而在测试阶段就能够通过ATPG(Auto Test Pattern General)自动生成测试向量,作为ATE的输入,同时产生期待值和ATE的输出比较,得到测试结果。完备的DGT设计可以提供高故障覆盖率的测试激励,保证芯片良率。

DFT的工作包括

-- 在项目初期规划DFT架构;

-- 在RTL级别设计测试电路;

-- 在验证阶段验证测试电路;

-- 在synthesis阶段实现测试逻辑的插入;

-- 在测试阶段提供测试向量

DFT能够缩短上市时间,降低测试费用,提高故障覆盖率(提高产品质量)

这些激励可以是直接的测试内容(Scan激励),也可以是触发芯片内部bist的激励。

· Scan设计

基于扫描设计是可测试性设计中最常用的一种方法。在综合阶段把普通触发器替换为既有扫描能力的触发器,即触发器的输入端增加了一个选择器,Select端是测试使能端。让后把替换后的触发器连接起来形成扫描链。

扫描设计分为两种:全扫描,部分扫描。

全扫描指把电路中所有的触发器替换为扫描触发器,并把他们连接在一起构成扫描链。

部分扫描是把只替换电路中的部分触发器。

扫描触发器会增加芯片面积(增加的选择器,以及布线复杂性),影响触发的延时。

而全扫描触发器可以采用组合ATPG工具生成测试模式,而部分扫描设计只能采用时序ATPG工具生成测试模式。时序ATPG工具相比组合ATPG,运行时间长几倍,需要内存也大几倍。

扫描设计增加了电路的可观测性,电路中插入扫描链后,所有时序单元的D端都是扫描可观的,Q端是扫描可控节点。

最初的扫描设计是为了解决时序电路的测试问题而提出的一种可测试性设计方法。进入测试模式后,选择Scan_in输入的激励,激励通过扫描链输出到Scan_out,输出如果满足期待值的话,就说明扫描链上的触发器都是没有缺陷器件。

随着技术的进步,扫描链被优化到能够为电路中的组合逻辑提供激励的加载通道和响应的观测通道。

扫描测试的时序

1)SE=1,进入扫描模式,通过扫描移位(shift)操作把设计中的时序单元设定为Scan_in输入的数值,扫描链的长度(Flip Flop的个数)决定了这个过程所需时钟cycle数。电路工作在扫描移动测试状态。

2)SE=0,电路工作在正常状态(capture),只法1cycle有效时钟触发,Scan_in输入值通过组合逻辑传到后级FF被Latch住。

3)SE=1,抓取电路组合部分的响应。电路工作在扫描移动测试状态(shift out)。把capture状态Latch的值通过移位传到Scan_out端进行期待值比较。

需要施加多个测试模式时,前一个测试响应移出电路的同时就移入当前测试激励。shift in和shift out同时进行。

如果不进行第二步的话,数据不会通过组合逻辑,只能检测扫描链上触发器的状态。

· 内建立自测试(BIST)Build in self test

内建自测试是可测性设计的另一种重要的方法。这种方法的基本思想是由电路自己生 成测试向量,而不是要求外部施加测试向量,它依靠自身逻辑来判断所得到的测试结果是否 是正确的,这样就大大降低了对测试设备的要求,而且它所要求“借用”的芯片封装引脚的 数目要少得多。内建自测试的基本原理如图所示。 BIST 又分为逻辑内建自测试(LBIST)和存储器内建自测试(MBIST),MBIST 又分为 RAMBIST 以及 ROMBIST。由于 BIST 要求电路自身生成测试向量,而随机逻辑的测试向 量生成是非常复杂,故逻辑内建自测试在实际中应用有限,最常用的是 MBIST。

RAMBIST

由于 RAM 可读可写,因此我们要从读和写两个方面对它进行测试,因 于 RAM 结构规整致密,故其测试向量不像普通电路测试向量那样复杂,RAM 测试的 关键在于施加测试向量的时序上,最常用的是 March 算法。

ROM与 RAM 最大的不同之处是 RAM 可读可写,而 ROM 只读不可写,ROM 中的信息是由制造厂家做好了的,因此 ROMBIST 与 RAMBIST 的最大不同就是前者没有向量生成电路, 由于ROM 中的信息是多种多样,故其响应分析是非常复杂的,通常要用特征分析 器首先对其响应进行压缩得出响应特征。

ROM BIST的作用有两个:一方面是要验证存储在ROM中的数据是否正确;另一方面是确保能够准确读出存储器中的信息,而不出现破坏性的读操作,即在进行读操作时不会改 变或毁坏数据。ROM测试也可以采用类似RAM测试的March算法。文章来源:https://www.toymoban.com/news/detail-641193.html

Tips:

[1]DFT的测试内容不同与功能性测试。

[2]功能性测试是为了验证设计出的是想要的;

[3]DFT测试是为了检测生产出的就是设计的。文章来源地址https://www.toymoban.com/news/detail-641193.html

到了这里,关于DFT基础知识整理的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA] 7系列FPGA的基础知识](https://imgs.yssmx.com/Uploads/2024/02/484166-1.png)