今天做了一个关于输入查找表(LUT)的题目,里面关于8-1 MUX的处理方式让我觉得非常的新奇。

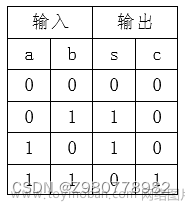

题目很简单,大意就是要求设计一个8位的移位寄存器,同时附加随机访问功能。也就是通过输入的ABC三个数字对应的二进制数转换为一个地址(很像存储中的方式),然后访问移位寄存器里面对应地址的数据。

但是这里关于寻址的处理方式很有趣。一般情况下,可能我自己会想到的是写一个case或者if-else的条件选择语句,但是即便是8位的移位寄存器,这个语句已经够长了,更不要说涉及到更多位存储的情况。

文章来源:https://www.toymoban.com/news/detail-642354.html

文章来源:https://www.toymoban.com/news/detail-642354.html

这个地方答案给出了一种巧妙的处理方式,基于ABC三个参数的8-1选择器可以直接用{A,B,C}的方式来进行定位。综合器会直接将其转化成对应的二进制数文章来源地址https://www.toymoban.com/news/detail-642354.html

到了这里,关于verilog 学习笔记(3)输入查找表(LUT)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!