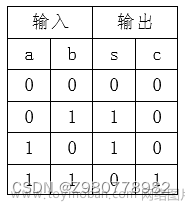

除以2可以这样移位

迭代除法,就是直接除

迭代除法,就是直接除

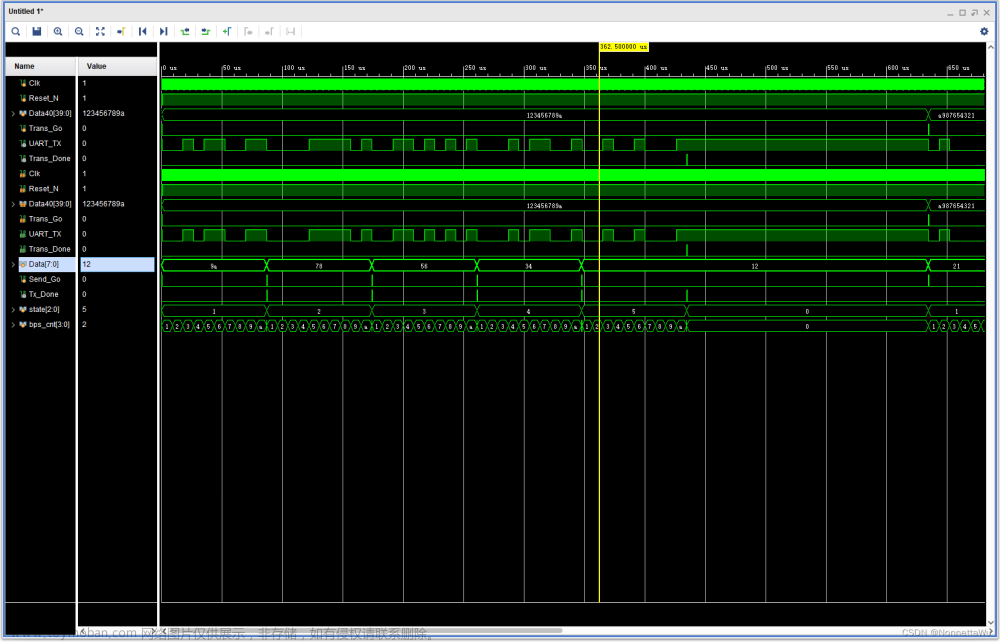

除数左移,被除数减去除数,余数大于0则商数置1然后左移,余数作为被减数左移,再减除数,再看余数是否大于0,若大于0,还是这样操作,若小于0,则商数为0,且余数直接等于上次的余数文章来源:https://www.toymoban.com/news/detail-642479.html

synplifypro自动对定点操作实现这类结构,对整数并自动地优化不利用位文章来源地址https://www.toymoban.com/news/detail-642479.html

到了这里,关于FPGA应用学习笔记----定点除法的实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!