前言

正文

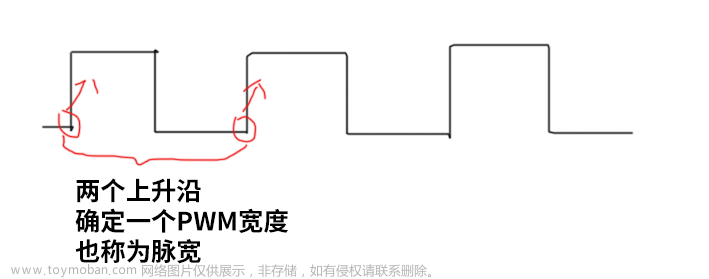

一、50%的占空比

目标:FPGA的时钟为50MHZ,生成20KHZ的占空比位50%的PWM波

设需要计数器计到x后清零,求出x:x/50_000_000 = 1/20_000

设计文件

module pwm #(

parameter MAX = 2499

)(

input clk,

input rst_n,

output reg clk_20k

);

reg [15:0] cnt;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 16'd0;

else if(cnt == MAX)

cnt <= 16'd0;

else

cnt <= cnt + 16'd1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

clk_20k <= 1'd0;

else if(cnt == (MAX -1) /2)

clk_20k <= 1'd1;

else if(cnt == MAX)

clk_20k <= 1'd0;

else

clk_20k <= clk_20k;

end

endmodule

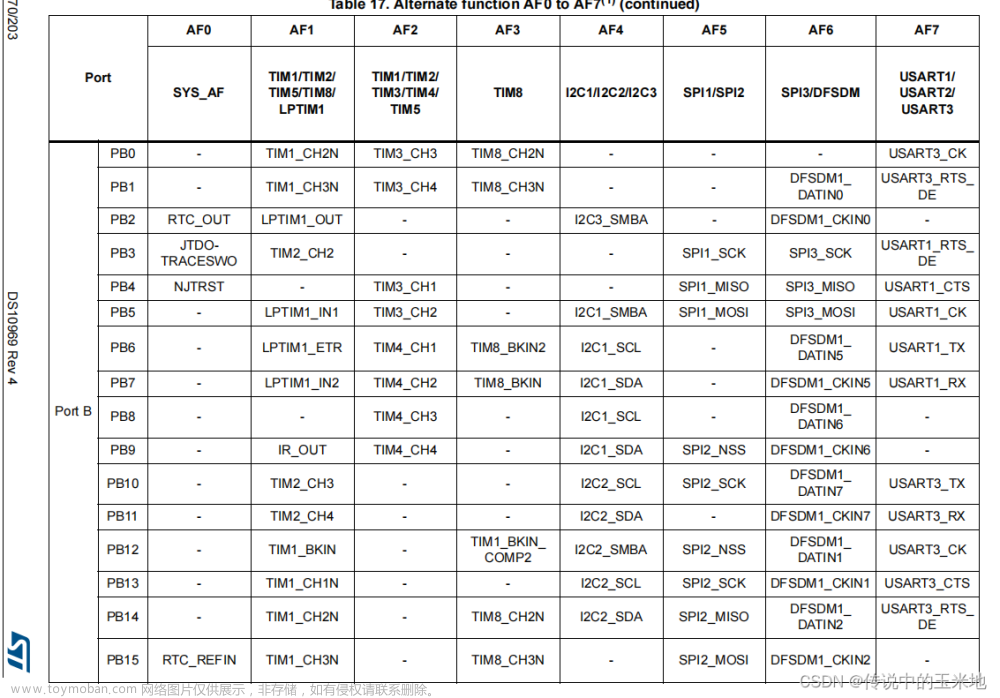

二、占空比可调

使用FPGA生成一个占空比为70%的PWM波

注:可以通过调节PWM_num 的大小,进而实现不同占空比的PWM波 文章来源:https://www.toymoban.com/news/detail-642749.html

文章来源:https://www.toymoban.com/news/detail-642749.html

// 占空比可变

module pwm_change #(

parameter MAX = 1249,

parameter PWM_num = 874

)(

input clk,

input rst_n,

output reg clk_20k_70

);

reg [15:0] cnt_1249;

reg dec_up;

reg dec_down;

// 生成三角波,使用if语句,实现自加到1249后,再自减到0

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_1249 <= 16'd0;

else if(dec_up)

cnt_1249 <= cnt_1249 + 16'd1;

else if(dec_down)

cnt_1249 <= cnt_1249 - 16'd1;

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

dec_up <= 1'd0;

dec_down <=1'd0;

end

else if(cnt_1249 == MAX)begin

dec_down <= 1'd1;// 计到最大值后,向下计数信号拉高

dec_up <= 1'd0;

end

else if(cnt_1249 == 0)begin

dec_down <= 1'd0;

dec_up <= 1'd1; // 计到最小值后,向上计数信号拉高

end

end

// 通过上面已经生成的三角波,使用PWM_num调节占空比

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

clk_20k_70 <= 1'd0;

else if(cnt_1249 >= PWM_num)

clk_20k_70 <= 1'd0;

else if(cnt_1249 < PWM_num)

clk_20k_70 <= 1'd1;

else

clk_20k_70 <= clk_20k_70;

end

endmodule

最后生成的70%占空比的PWM波形如下: 文章来源地址https://www.toymoban.com/news/detail-642749.html

文章来源地址https://www.toymoban.com/news/detail-642749.html

到了这里,关于FPGA:生成占空比可调的PWM波的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FOC-Stm32]设置PWM占空比(比较值)的几种方法](https://imgs.yssmx.com/Uploads/2024/02/553261-1.png)