引言

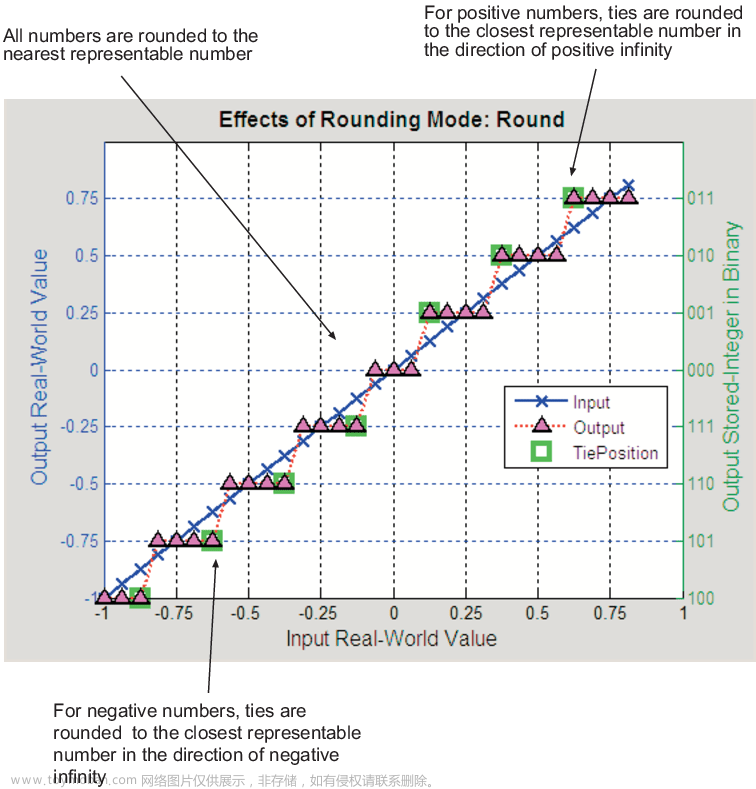

浮点数转换定点数是一种常见的数值转换技术,用于将浮点数表示转换为定点数表示。浮点数表示采用指数和尾数的形式,可以表示较大范围的数值,但存在精度有限的问题。而定点数表示则采用固定小数点位置的形式,具有固定的精度和范围。在某些应用中,特别是在嵌入式系统和数字信号处理领域,使用定点数表示可以更加高效地进行计算。然而,很多算法和库函数都是基于浮点数实现的,因此需要将浮点数转换为定点数才能在这些系统中使用。浮点数转换定点数的背景涉及到浮点数和定点数的表示方法、精度要求以及性能考虑等方面。在转换过程中需要考虑相应的位宽、小数点位置、舍入方式等参数的选择,以保证转换后的定点数能够准确地表示原始浮点数,并满足应用的要求。此外,浮点数转换定点数也可能涉及到溢出、舍入误差、舍入方式选择等问题。因此,在实际应用中需要仔细分析和评估转换算法的性能和精度,并根据具体的应用场景进行调整和优化。文章来源:https://www.toymoban.com/news/detail-643822.html

背景

浮点数转换定点数的概念和技术并没有一个具体的发明者或起源人。它是在计算机科学和数字信号处理等领域的发展过程中逐渐形成和应用的。浮点数和定点数的概念最早可以追溯到计算机科学的早期发展阶段。在计算机领域的先驱们,如冯·诺依曼、约翰·冯·诺伊曼、阿兰·图灵等,对于数字表示和计算方法进行了深入研究,为后来的浮点数和定点数概念的发展奠定了基础。随着计算机技术的快速发展,浮点数和定点数的表示方法和转换技术也得到了更多的研究和应用。在数字信号处理领域,特别是在嵌入式系统和通信领域,浮点数转换定点数被广泛应用于各种算法和信号处理任务。因此,浮点数转换定点数作为一种技术和方法,并没有一个特定的发明者或起源人,而是在计算机科学和数字信号处理领域的长期积累和发展中形成的。不同的研究者和工程师在不同的应用场景中对该技术进行了不同的改进和优化,推动了该技术的应用和发展。文章来源地址https://www.toymoban.com/news/detail-643822.html

软核开发

到了这里,关于中科亿海微浮点数转换定点数的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!