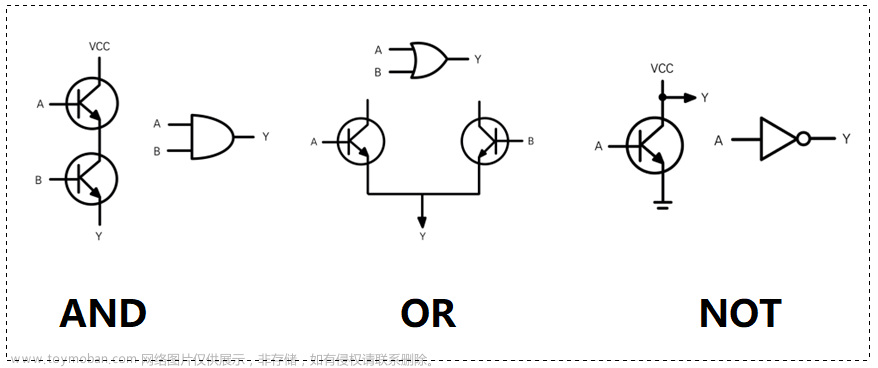

0x00 回顾:AND/OR/NOT 逻辑的特性

AND:与门可以具有两个或更多的输入,并返回一个输出。当所有输入值都为 1 时,输出值为 1。如果输入值中有任何一个为 0,则输出值为 0。

OR:或门可以具有两个或更多的输入,并返回一个输出。如果输入值中至少有一个为 1,则输出值为 1。如果所有输入值都为 0,则输出值为 0。

NOT:非门具有一个输入和一个输出。当输入值为 1 时,输出值为 0;当输入值为0时,输出值为1。

晶体管级逻辑门 AND/OR/NOT 的结构:

0x01 扇出的概念(Fan-out)

扇出 (fan-out) 是一个定义单个逻辑门能够驱动的数字信号输入最大量的专业术语。文章来源:https://www.toymoban.com/news/detail-644799.html

扇出即输出可从输出设备输入信号的电路的数量。它的英文含义是“分散”。扇出的大小表示一个输出被多个其他逻辑门的输入使用。如果删除太大,电路可能会受损或信号无法正确传递,因此需要解决这个问题。可以通过将一个信号分割为两个部分进行处理或创建缓冲区等方法来减小扇出的影响。文章来源地址https://www.toymoban.com/news/detail-644799.html

0x02 传

到了这里,关于FPGA实践 ——Verilog基本实验步骤演示的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!