PL部分

一、新建工程:

现开发板型号为xc7z100ffg900-2

- 选择芯片(选择芯片7100的话,就输入xc7z100 后面的-1和-2是速度等级),更改项目名为system。

- Create Block Design(创建模块化的设计)——>设置设计名称为system。

这时会出现design窗口和source窗口、画布窗口,source中出现.bd后缀的文件system.bd,这个就是我们创建的block design(bd缩写)。

- 在画布点击“+”,选择查找zynq7000,会出现“zynq7 processing system”双击打开,就会出现一个“zynq7 processing system”模块示意图。

- 双击进入,然后可以对ZYNQ7 Processing System IP核进行配置。

二、配置界面

- DDR配置:

在DDR Configuration中完成DDR控制器的配置,DDR型号要与开发板相符:

如果没有相应的型号就选参数兼容的芯片型号或者custom

记住DDR3型号的方式:

某7020开发板的两个DDR3型号是:MT41J256M16-125,MT是美光的芯片,256M,位宽16bit。

存储容量是:256M*16bit*2片DDR3=8192Mbit=8Gbit

- MIO与EMIO配置

(1)在Peripheral I/O Pins中设置UART

具体选择哪个UART,要看开发板硬件设计,看原理图,找到核心芯片ps上uart_rx和uart_tx,发现引脚为“PS_MIO49_501_D18”和“PS_MIO48_501_C19”,所以UART的引脚应该为49和48引脚。选中Peripheral I/O Pins中的这两个引脚(7100对应了UART1)。

(2)设置UART的波特率:在PS-PL Configuration中的“general”设置UART1的波特率。目前选择默认的115200.

(3)也可以在MIO Configuration中设置UART和其他IO口,但是没有Peripheral I/O Pins中设置直观

在MIO Configuration中可以设置IO引脚的参数:

- 可以看到UART的tx和rx是固定不能更改的。

- Bank I/O Voltage(引脚电压),电压设置也要查原理图。

在原理图中BANK500(即BANK0)、BANK501(即BANK1)上有电压值,有时两个电压值是不一样的,现用的7100是两个都是1.8V电压。

以上设置完一个最小系统,点击ok,到画布界面。

- 回到画布界面

画布上点开“FIXED_IO”上的“+”,可以看到MIO,UART就是在MIO(共54个引脚)中。

- 删除PS上多余的接口

双击ps IP核打开配置界面。

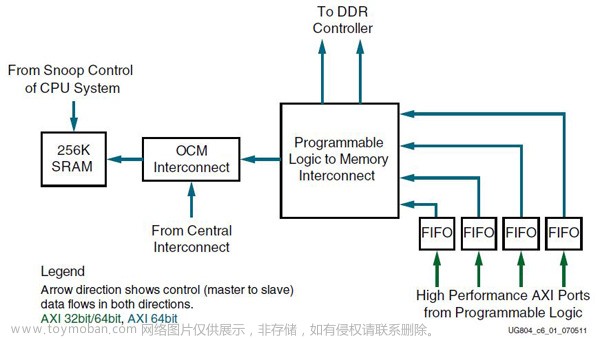

除了上面的DDR和MIO是PS 的接口,其余的都属于PS和PL之间的接口。

- 在PS-PL Configuration中点开第二项“AXI Non……”,再展开“GP Master……”,把对勾取消。这时画布上ps IP核上的M_AXI_GP0和M_AXI_GP0_ACLK(名字前面一致,都属于M_AXI_GP0)

- FCLK_CLK0是ps提供给pl的时钟信号,同样双击打开配置界面,点开Clock Configuration。

- 首先,PS要配置一个时钟,点开processor/memory clocks,配置CPU和DDR的时钟。原时钟是在上面,有个input frequency,在原理图上的核心板上找到原时钟。在原理图的BANK500上有个PS_CLK连接了一个33.33333MHz的晶振。

原时钟经过两个锁相环(ARM PLL和DDR PLL)进行配平得到时钟。

- 往下找到PL Fabric Clocks时钟,默认FCLK_CLK0是勾选的,取消勾选,这时该接口就没有了。

- FCLK_RESET0_N是ps提供给pl的复位接口。在PS-PL Configuration中的“general”往下拉,有个“Enable Clock Resets”,将FCLK_RESET0_N的对勾取消。

以上,多余的接口就取消了。PS接口配置完成。

在画布左上角有个蓝色“run block automation”,点击,再点击ok。

此时就会自动创建出两个端口。

扩展出来的接口就可以连接到器件的引脚上去,从而给器件外面的设备(像DDR存储器),进行交互

- 验证硬件系统

画布上面一行有个打“√”的按键,叫“validate design”,点击进行一个初步的验证(不能完全保证设计正确)。

在source中的“system.bd”右击鼠标,选择“generate output product”。(该步骤是为了把设计产生一个输入输出的结果,比如对设计产生管教约束,或者对一些ip核,进行综合和实现)。选择“out of context per IP”(为每个IP核产生一个独立的输出)。

在source的下面点击IP Sources中产生了三个文件。

- 生成硬件描述的顶层文件(HDL)。

在source中的“system.bd”右击鼠标,选择“create HDL wrapper”。相当于要用硬件描述语言把我们刚才所完成的设计封装起来。选择默认选项,也就是说用vivado去管理封装之后的文件,这样生成的顶层文件就会自动进行更新,也就不需要让我们进行这样的过程了。

完成之后在source上出现了“system_wrapper”文件,后缀名是.v,也就说使用的virlog设计语言。

以上就设计完所有硬件部分。

因为上面都只是配置PS部分,没有设计PL部分,所以不需要生成bit流。直接导出SDK。

- 导出到SDK

- File->export->export hardware...

因为没有硬件,弹出的对话框中不勾选include bitstream,路径默认当前路径,点击ok。

运行后当前工程下多了一个.sdk的文件夹,里面有个.hdf文件,这就是刚才生成的硬件定义文件(实质上是zip格式的文件,可以用winrar解压打开,里面有很多子文件。其实不需要用解压工具打开,直接走下一步file->launch SDK)

- file->launch SDK

选择默认的“当前目录”文章来源:https://www.toymoban.com/news/detail-646790.html

打开后可以看到platform_0里面的文件就是上面用winrar解压打开的.hdf里的文件。其实sdk就是自动把刚才的.hdf解压,解压到system_wrapper_hw_platform_0这个文件夹中。这里面都是硬件信息。文章来源地址https://www.toymoban.com/news/detail-646790.html

到了这里,关于zynq7000学习(1)——vivado环境下PL配置的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!