时钟域就是同一个时钟的区域,体现在laways语句边缘触发语句中,设计规模增大就会导致时钟不同步,有时差,就要设计多时钟域。

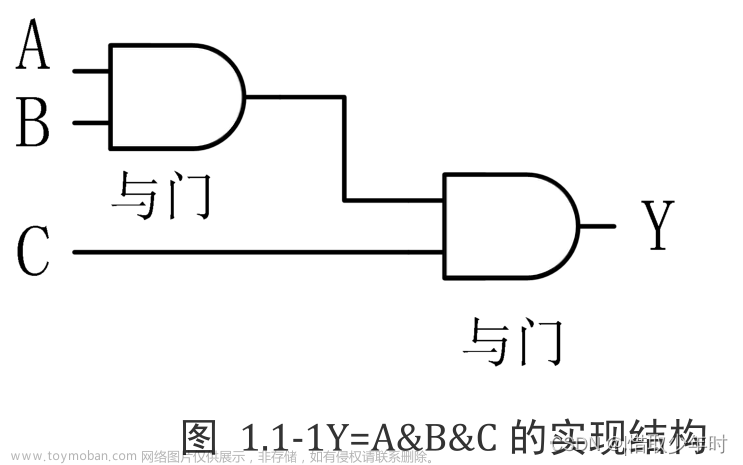

会经过与门的延时产生的新时钟域,这种其实不推荐使用,但在ascl里面很常见

在处理时钟域的信号传递,一般会有故障具有随机性,不同工艺出现问题的可能性不同,对于亚稳态的检测很少,故障很难被发现,要设计中要注意。

要经过组合延时,就会起冲突,间隔不够

数据要保证建立时间和保持时间才有效,RTL级无法分析亚稳态的,在门级都很难,提高设计本身的设计!,通过DLL或者PLL控制相位,来达到相位匹配,消除亚稳态。要保持时钟具有整数倍关系

若两个时钟毫无关系,或者FPGA为两个系统提供接口时候,很难使用相位控制

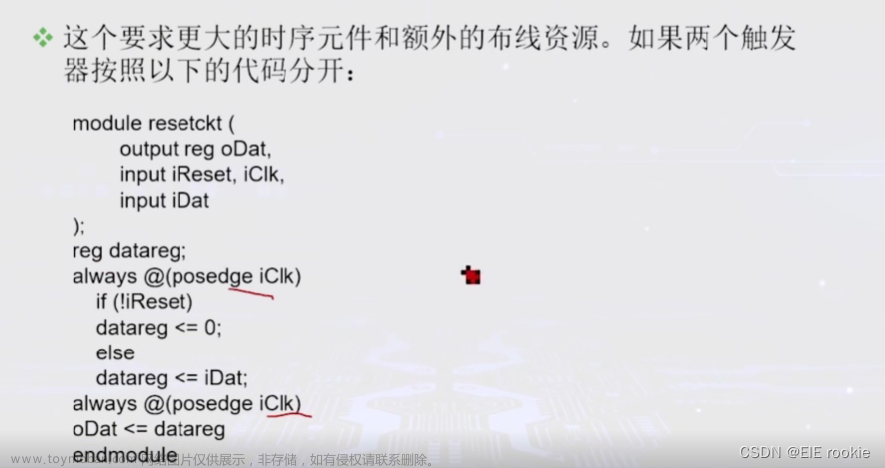

用打两拍的方法,解决单bit的亚稳态问题

FIFO先入先出结构解决多bit数据

用fifo存储数据,然后根据时钟2调整推出数据,要注意防止溢出,要有效握手控制,满标志通知发送端已经满了,空标志通知接收端已经没有数据可以抓取了,

文章来源:https://www.toymoban.com/news/detail-647145.html

文章来源:https://www.toymoban.com/news/detail-647145.html

读状态机的示意图,写状态机类似。 文章来源地址https://www.toymoban.com/news/detail-647145.html

到了这里,关于FPGA应用学习笔记--时钟域的控制 亚稳态的解决的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!