一、设计目的

1、掌握分频器的设计原理;

2、用HDL语言设计分频器。

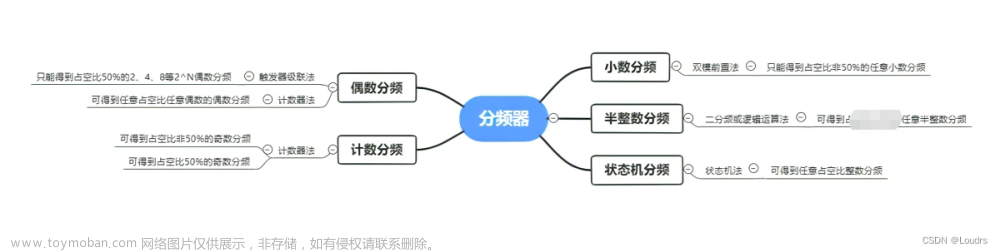

二、设计原理

分频器与计数器类似,也是要对时钟脉冲进行计数,但其输出的不是对时钟脉冲个数的计数值,而是其频率与时钟的频率成固定比例关系的脉冲信号。整数分频是所有分频器中最简单,最容易实现的。我们只需要通过计数器计数就完全可以实现。如整数N分频,就可以通过待分频的时钟触发计数器计数当计数从0计数到N/2-1时,输出时钟进行反转,并使计数器在下一个时钟从0开始重新计数,如此循环就可以实现任意的等占空比或占空比近似为50%的整数分频。图2-12就是一个占空比为50%的6分频器的仿真波形。

上图为占空比为50%的6分频器波形

三、设计内容

设计一个分频输出信号的占空比近似为50%的分频器,将50MHz输入时钟分频为1Hz时钟,在试验箱EXT_B_A1_1端口输出,并用示波器观察输出波形。所用引脚如下表所示。

| 芯片引脚 |

开发平台模块 |

| P25 |

CLK(50MHz) |

| E25 |

EXT_B_A1_1 |

四、设计结果

1、分频器源程序:

module FPQ(clk_out,clk_in,rst);

output clk_out;

input clk_in;

input rst;

reg [25:0] cnt;

reg clk_out;

parameter N=50000000;

always @ (posedge clk_in or negedge rst)

begin

if(!rst)

begin

cnt <= 0;

clk_out <= 0;

end

else begin

if(cnt==N/2-1)

begin clk_out <= !clk_out; cnt<=0; end

else

cnt <= cnt + 1;

end

end

endmodule2、仿真波形图:

上图为6分频结果。

上图为50M分频结果,由于仿真时钟波形不够显示50000000次时钟波形,所以分频结果未显示出。

3、管脚约束:

4、下载到试验箱上的结果:

上图为按下复位键的结果:LED0不闪烁。

上图为按下复位键的结果:LED0不闪烁。

文章来源:https://www.toymoban.com/news/detail-648490.html

文章来源:https://www.toymoban.com/news/detail-648490.html

上图为松开复位键的结果:LED0每隔一秒亮或灭一次,证明时钟50MHz被成功分频为1Hz。文章来源地址https://www.toymoban.com/news/detail-648490.html

到了这里,关于FPGA设计开发(基础课题):分频器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!