典型电路设计之片内存储器的设计之RAM的Verilog HDL描述一

RAM是随机存储器,存储单元的内容可按需随意取出或存入。这种存储器在断电后将丢失所有数据,一般用来存储一些短时间内使用的程序和数据。

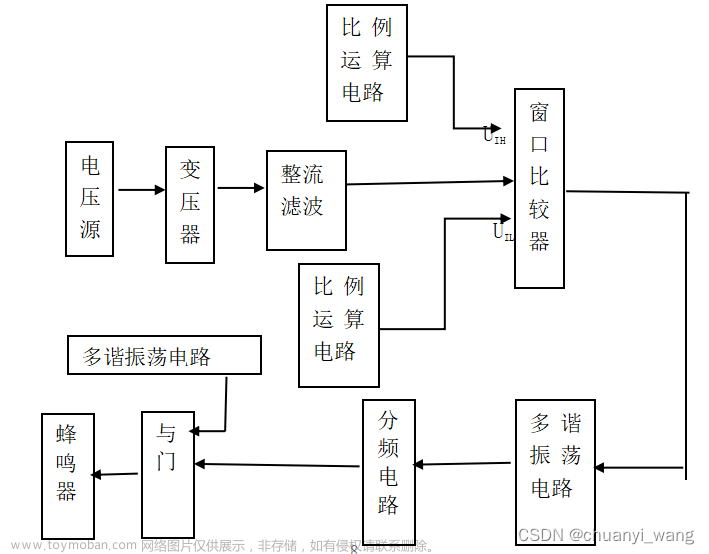

其内部结构如下图所示:

例:用Verilog HDL 设计深度为8,位宽为8的单端口RAM。

单口RAM,只有一套地址总线,读和写操作是分开的。

下面是verilog代码文章来源:https://www.toymoban.com/news/detail-654621.html

module ram_single( clk, addm, cs_n, we_n, din, dout);

input clk;

input [2:0]addm;

input cs_n;

input we_n;

input [7:0] din;

output[7:0] dout;

reg [7:0] dout;

reg [7:0] raml [7:0];

always@(posedge clk)

begin

if(cs_n)

dout<=8'bzzzz_ZZZZ;

else

if(we_n)

dout<=raml[addm];

else

raml[addm]<=din;

end

endmodule

下面是testbench文章来源地址https://www.toymoban.com/news/detail-654621.html

module ram_single_tb;

reg clk, we_n, cs_n;

reg [2:0]addm;

reg [7:0]din;

wire [7:0]dout;

ram_single U1(.clk(clk),.addm(addm),.cs_n(cs_n),.we_n(we_n),.din(din),.dout(dout));

initial begin

clk=0;

addm=0;

cs_n=1;

we_n=0;

din=0;

#5 cs_n=0;

#315 we_n=1;

end

always

#10 clk=~clk;

initial

begin

repeat(7) begin

#40 addm=addm+1;

din=din+1;

end

#40 repeat(7)

#40 addm=addm-1;

end

endmodule

到了这里,关于【【典型电路设计之片内存储器的设计之RAM的Verilog HDL描述一】】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!