1、set_input_delay的本质

set_input_delay是对模块input信号在模块外部延迟的约束,本质上EDA工具会根据约束调整设计内部的器件类型,摆放的位置以及优化内部组合逻辑保证满足约束要求。

约束指导原则:尽量照顾设计外部逻辑延时

set_input_delay -max delay_vaule 中delay_vaule 数值尽量大

set_input_delay -max delay_vaule : delay_vaule 数值越大,对自身的约束越严格,对外部的要求越宽松,本质上是对setup time的约束。

set_input_delay -min delay_vaule : delay_vaule 数值越小,要求自身有足够的延时,能够cover住hold time,本质上是对hold time的约束。delay_vaule 为0 表示要求input 信号的自身的延时至少要大于hold time的。

2、set_input_delay示意图

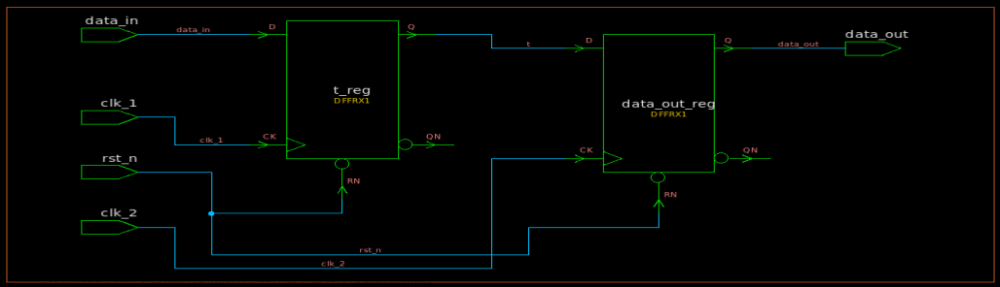

图7-21显示了DUA(the design under analysis )的输入路径。触发器UFF0在DUA外部,并向DUA内部的触发器UFF1提供数据。数据通过输入端口INP1连接。触发器UFF0和触发器UFF1的采样时钟均为CLKA。不考虑CLKA时钟偏移,该时钟周期是两个触发器UFF0和UFF1之间采样时间差。外部逻辑的delay有Tclk2q(即启动触发器UFF0的CK到Q延迟)和Tc1(即通过外部组合逻辑的延迟)。针对DUA输入管脚INP1设置的set_input_delay指的就是相对于时钟CLKA的Tclk2q+Tc1延时。假设CLKA的时钟周期为2ns,Tclk2q+Tc1延时为1.5ns,则INP1引脚的逻辑在设计中只有500ps(=2ns-1.5ns)可用于内部传播,即UFF1的Tc2加Tsetup必须小于500ps,才能保证触发器UFF1可靠地捕获由触发器UFF0输出的数据。

文章来源地址https://www.toymoban.com/news/detail-654824.html

3、set_input_delay 简单案例

如图7-22所示Tclk2q的延时范围为0.8ns~1.1ns,组合逻辑Tc1的延时为2.2ns~5.6ns,此时Tclk2q+Tc1 最大延迟为6.7ns(=1.1ns+5.6ns)。最小延迟为3ns(=0.8ns+2.2ns)。请注意,这些延时都是相对于时钟采样沿设置的。我们用-max和-min参数描述最大延时和最小延时。-min 3.0 要求INPA内部时延加上3ns能够大于hold time,-max 6.7要求INPA内部时延加上Setup time要求小于8.3ns(=15-6.7)

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

文章来源:https://www.toymoban.com/news/detail-654824.html

文章来源:https://www.toymoban.com/news/detail-654824.html

到了这里,关于浅谈时序:set_input_delay的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!