DVP接口的调试总的来说可以分为2种,一种是AHD芯片转DVP接口的调试,例如tp9930,nvp6158,xs9922a(芯晟)等;另一种就是普通sensor转dvp接口,类似gc2145或FPGA,调试的dvp接口常见的是BT601/BT1120/BT656。

针对dvp接口摄像头的调试,首先要确认是否有外同步即vsync/hsync,一般BT656/BT1120是内同步的,即没有vsync/hsync;硬件上要先确保mclk和pclk正常的输出,BT601常见的mclk是SOC提供的,而BT656/BT1120是接外部时钟提供27/24M给芯片。vsync和hsync的频率是很低的,测量过一次,当时vsync的频率是34HZ,而hsync的频率是52Khz。

文章来源地址https://www.toymoban.com/news/detail-656465.html

1.BT1120/BT656

DVP固定是高对齐采集数据;并且一般8bit的是bt656接口,16bit是bt1120接口;像隔行or逐行输入都支持。cvbs是隔行信号,分辨率为720x576,960x576(PAL制)或者720X480,960x480(NTSC制)。isp对于隔行信号要求是宽32位对齐,不然就会导致丢失一些pixel,从而出现类似绿条纹的现象。所以720x480的分辨率可以走cif,不走isp。

BT656: 驱动里的querystd函数,一般将接口配置为V4L2_STD_PAL;

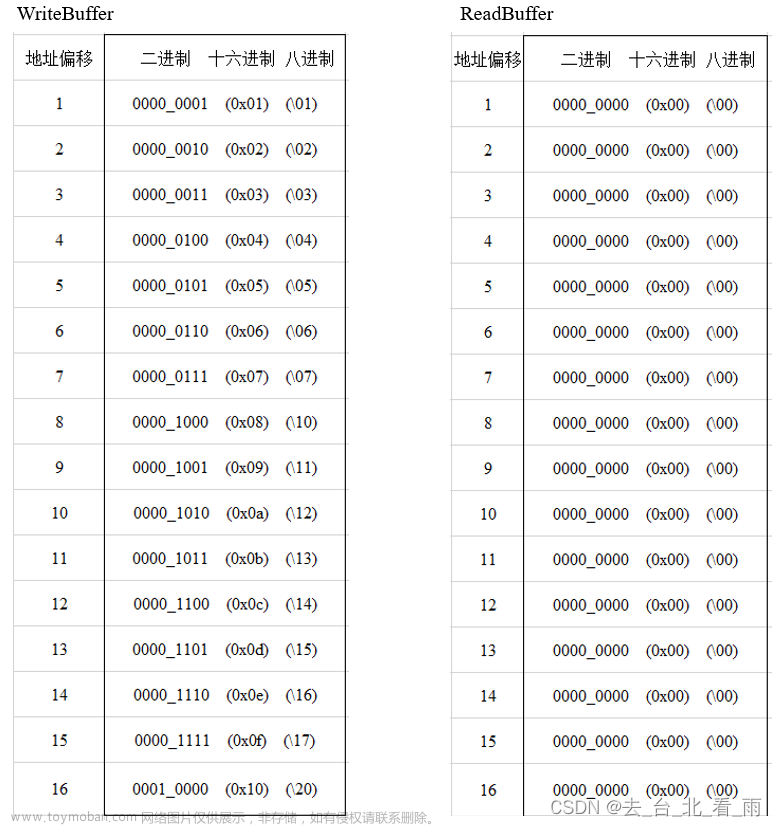

BT1120: 驱动里的querystd函数,一般将接口配置为V4L2_STD_ATSC; BT1120和BT656是支持单沿或双边沿采样的(redmine376971)。在dts配置方面记得data引脚的复用。当然BT601也是高位对齐,所以在检查硬件原理图时,一定要和下面这表对上

下面客户的硬件原理图接法明显错误,没有按照上表所示,实现高8bit对齐,所以会出现抓图时可以打印出帧率,但画面是异常的,例如全粉之类的;按如下接法去修改硬件,重新打板。

2.AHD转DVP接口

dts的链路配置其实和普通sensor是一样的,直接sensor->rkcif_dvp,一般不需要接入isp;在保证底层正常出流后,由于其走的是usb camerahal,所以还要配置下external_camera_config.xml,使用dumpsys media.camera查看上层是否识别到设备,由于AHD是接4路的摄像头,有4个cameraid,所以dumpsys下会识别到4个设备。

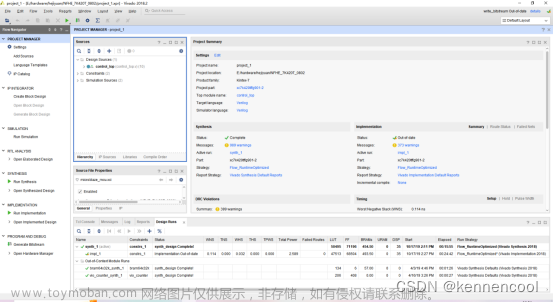

由于默认的vicap代码仅支持CameraHal3框架,不支持适配Android usb camerahal框架,所以需要修改vicap代码进行适配。3588平台,就不需要修改vicap代码了,因为驱动已经支持了,直接在dts中配置上该属性即可。

3.桥接芯片或fpga转DVP接口

这个就使用万能模板gc2145,所有的dvp摄像头调试的驱动,都可以在这个基础上进行修改的;以fpga转bt1120为例子,fpga是不用带寄存器的,也就是没有i2c读写操作,上电就是直接输出数据的。

例如客户调试bt1120这种,要注意客户的数据,不能带FF这种影响同步,正常来说bt1120设备是不会有的,就是FPGA这种才会碰到。

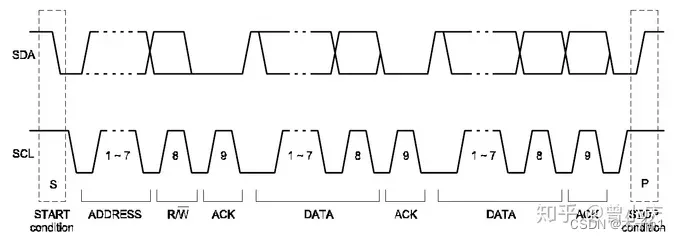

FPGA转bt1120,一般是16根数据线,一根时钟线,还有同步信号EAV和SAV;针对bt1120,每一行在视频传输中的格式,在定时基准码的前三个字节是恒定的FF 00 00,第四个字节XY是需要我们分析的。正常来说bt1120传输yuv都是limit range,y数据范围16-235,uv范围是16-240;有时候没有限制就会出现异常(控制器采集可能没有限制),例如报dvp相关的错误overflow或size err;所以视频源端在BT1120输出时序端不做修改、仅对高8bit和低8bit的数值进行限制,板卡端就能正常采集(高8bit传输Y分量、低8bit传输UV分量)。

4.hdmiin转转dvp

356x平台驱动的移植可以参考下lt8619,里面需要有寄存器的操作;8619是转bt1120或bt656,这边g_mbus可以看出;bt1120可以是单边沿或双边沿。

5.常遇到的问题

5.1 概率性图像错位

hdmi转bt1120,会概率性图像错位和画面颜色显示异常;出错时有如下报错;其实overflow也就是一帧没结束,下一帧就来了;可以降低帧率或提高ddr去解决。

rkcif_dvp: dvp overflow err

rkcif_dvp: ERROR: DVP_ALL_ERROR_INTEN:0x4205.2 热插拔出现花屏

dvp接口进行热插拔,对于dvp输出画面会有极大概率出现错开或者花屏的现象;capture文件的rkcif_stop_streaming中强制执行rkcif_do_cru_reset,热插拔画面就不会出现问题。

5.3 v4l2取图卡住

bt656可以是单通道的输出或多通道输出,发送端输出是单通道还是2通道还是4通道的数据,这个需要确认下,一般在AHD芯片的初始化参数中是有配置好channel id的;例如遇见客户将ahd芯片配置成单通道,单边沿采样是可以出图的,但是配置成双通道,双边沿采样则无法出图,如下图所示tp9963 bt656双通道输出时序格式如下,上升沿传输通道1,下降沿传输通道2;这个无法出图如上述说的,初始化参数没有配置channel id,添加后2通道可以正常出图。(针对新的转换芯片)

5.4 抓图时overflow刷屏

TP9930转dvp bt1120,抓图时1080p出现如下报错;使用720p抓图时,没有报错;首先要先确认是使用了TP的color bar还是外接了AHD摄像头,接的AHD摄像头是否是对应的分辨率;TP的color bar,配置的是测试模式#define TECHPOINT_TEST_PATTERN 1,所以正确应该是输出蓝屏的。

rkcif_dvp: dvp overflow err

rkcif_dvp: ERROR: DVP_ALL_ERROR_INTEN:0x20!!TP9930在1080p25fps下报overflow错误,在提高ddr频率 / 提高vicap优先级 / 增大vblank无效的情况下,可以联系下TP原厂的FAE,问问怎么调整TP9930输出的相位,因为可能不同的VC通道其相位不同,导致异常。如下是TP9930输出调整相位图;(CLK Delay Control I/II Register)所以参考0xF2/F3的说明,修改9930驱动中的0xF2/F3寄存器的配置,值一点点调整试试。

后面1080p抓帧报错,把0xF2/0xF3的值从0x77改成0x7f,4个video节点抓图都正常,没有报错了。

文章来源:https://www.toymoban.com/news/detail-656465.html

文章来源:https://www.toymoban.com/news/detail-656465.html

到了这里,关于camera之dvp接口介绍与调试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!