搭建EDA环境

参考如下博文安装Synopsys EDA开发工具

https://blog.csdn.net/tugouxp/article/details/132255002?csdn_share_tail=%7B%22type%22%3A%22blog%22%2C%22rType%22%3A%22article%22%2C%22rId%22%3A%22132255002%22%2C%22source%22%3A%22tugouxp%22%7D

Synopsys EDA工具的结构

下面使用Synopsys的EDA数字综合仿真工具直观感受以下数字设计的基本流程:

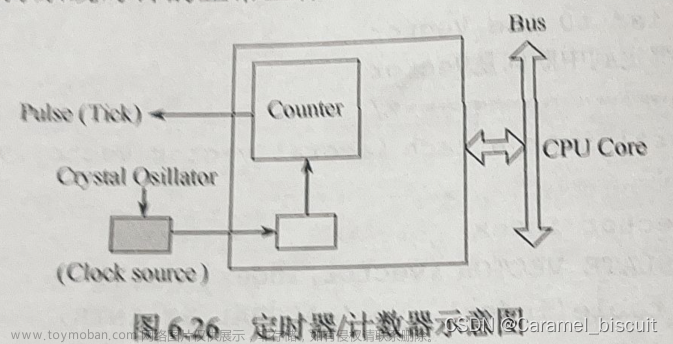

数字模块设计&仿真

counter_tb.v

`include "timescale.v"

module counter_tb;

reg irst = 0;

reg iclk = 0;

wire [3:0] ocnt;

initial begin

irst = 1; #100;

irst = 0; #300;

$stop;

#1000;

$finish;

end

always begin #5 iclk = !iclk; end

counter counter_test(

.irst(irst),

.iclk(iclk),

.ocnt(ocnt)

);

initial

$monitor("At time %t, ocnt = %d", $time, ocnt);

initial

begin

//$dumpfile("counter_test.vcd"); //$dumpvars(0, counter_test);

$fsdbDumpfile("counter_tb.fsdb"); //testbench的名字

$fsdbDumpvars();

$fsdbDumpSVA();

$fsdbDumpMDA();

end

endmoduletimescale.v

`timescale 1ns/1pscounter.v

`include "timescale.v"

module counter(irst, iclk, ocnt );

input irst, iclk;

output reg [3:0] ocnt;

always @ (posedge iclk)

if(irst)

ocnt <= 4'b0000;

else

ocnt <= ocnt + 1'b1;

endmoduleMakefile

all:

iverilog -o counter_test $(notdir $(wildcard ./*.v))

vvp -n counter_test -lxt2

cp counter_test.vcd counter_test.lxt

sim:

gtkwave counter_test.lxt

vcs:

vcs -R -full64 -timescale=1ns/1ns -fsdb -f file.l

verdi:

verdi -f file.l -ssf counter_tb.fsdb

clean:

rm -fr *.lxt *.vcd

rm -fr counter_testfile.l 是verilog源码清单文件:

counter_tb.v

counter.v

timescale.vVCS编译&综合,执行make vcs:

vcs -R -full64 -timescale=1ns/1ns -fsdb -f file.l

verdi查看波形,q退出ucli%,执行make verdi,实际上是执行如下命令查看波形:

verdi -f file.l -ssf counter_tb.fsdbUnified Command Line Interface (uCLi) 提供了与VCS交互仿真的控制命令,即与VCS的命令行输入接口。uCLi的命令是基于Tcl脚本语言进行编写的,也就是说可以编写Tcl脚本来实现:

- 控制仿真

- dump fsdb或者vpd波形文件

- 保存或恢复仿真状态

- force或release某个信号

- 使用breakpoints或scope以及内建宏等信息对设计进行调试

因此可以很灵活的进行调试和仿真控制。

波形和GTKWAVE得到的波形是一样的:

FSDB全称是Fast Signal DataBase,是 Verdi 支持的波形文件,一般较小,使用较为广泛。

fsdb文件是verdi使用一种专用的数据格式,类似于VCD(Value Change Dump),但是它是只提出了仿真过程中信号的有用信息,除去了VCD中信息冗余,就像对VCD数据进行了一次huffman编码。因此fsdb数据量小,而且会提高仿真速度。VCD文件是文本格式的文件,它是使用verilog内置的系统函数来实现的,是 Verilog HDL语言标准的一部分,因此所有的verilog的仿真器都能够查看该文件,允许用户在verilog代码中通过系统函数来dump VCD文件。

使用VCS提供的工具fsdb2vcd可以将fsdb格式的波形文件转换为VCD格式,之后再用gtkwave查看,转换命令如下,下图是FSDB转换为VCD格式的波形文件后的显示效果:

fsdb2vcd counter_tb.fsdb | tee a.vcd 文章来源:https://www.toymoban.com/news/detail-657296.html

文章来源:https://www.toymoban.com/news/detail-657296.html

参考资料

https://www.cnblogs.com/lzhj/p/15719777.html文章来源地址https://www.toymoban.com/news/detail-657296.html

结束

到了这里,关于Synopsys EDA数字设计与仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!