一. CoreMark简介

CoreMark是一款用于评估CPU性能的基准测试程序,它包含了多种不同的计算任务,包括浮点数、整数、缓存、内存等方面的测试。CoreMark的测试结果通常被用来作为CPU性能的参考,它可以帮助开发人员和系统管理员评估不同处理器和系统的性能,比较不同处理器之间的性能差异,也可以用来测试处理器在多线程并行计算方面的性能。

官网地址:

https://www.eembc.org

二. 平台环境

[硬件参数]

处理器: 算能SG2042 x 1

核心数: 64核

L1 Cache: I:64KB and D:64KB

L2 Cache: 1MB/Cluster

L3 Cache: 64MB System Cache

DRAM: DDR4 16Gx4

[软件环境]

linux版本: 22.10

gcc版本: 10.2.0

三. 获取源码

EEMBC将CoreMark源码托管在GitHub上,可以访问以下链接获得源码;也可以通过git命令下载到本地。

链接

https://github.com/eembc/coremark

四. 编译

本次采用的编译器是支持RVV的编译器,在我们的体验机器上已经完成了部署,可以通过文章下方的联系方式进群体验。

1:首先需要修改core_portme.mak文件,(在LFLAGAS_END变量添加-lpthread)

2:添加编译参数:-march=rv64gcv0p7_zfh_xtheadc -mabi=lp64d -mtune=c920。

添加完成后效果如下:

# Flag: CC

# Use this flag to define compiler to use

CC = gcc

# Flag: CFLAGS

# Use this flag to define compiler options. Note, you can add compiler options from the command line using XCFLAGS="other flags"

PORT_CFLAGS = -O3

#===============================Alter by me===========================

PF_CFLAGS = -march=rv64gcv0p7_zfh_xtheadc -mabi=lp64d -mtune=c920

FLAGS_STR = "$(PORT_CFLAGS) $(XCFLAGS) $(XLFLAGS) $(LFLAGS_END) $(PF_CFLAGS)"

CFLAGS = $(PORT_CFLAGS) $(PF_CFLAGS) -I$(PORT_DIR) -Iposix -I. -DFLAGS_STR=\"$(FLAGS_STR)\"

#===============================Alter by me===========================

# Flag: NO_LIBRT

# Define if the platform does not provide a librt

ifndef NO_LIBRT

#Flag: LFLAGS_END

# Define any libraries needed for linking or other flags that should come at the end of the link line (e.g. linker scripts).

# Note: On certain platforms, the default clock_gettime implementation is supported but requires linking of librt.

#===============================Alter by me===========================

LFLAGS_END += -lrt -lpthread

#===============================Alter by me===========================单核编译

ubuntu@perfxlab:/public/benchmark/coremark$ make compile XCFLAGS="-DMULTITHREAD=1 -DUSE_PTHREAD"多核编译

ubuntu@perfxlab:/public/benchmark/coremark$ make compile XCFLAGS="-DMULTITHREAD=64 -DUSE_PTHREAD"五. 在SG2042上执行coremark

1. 单核测试结果如下:

2. 64核测试结果如下:

六. CoreMark分数排行榜

SG2042 的64核跑分结果为:692303.531830 ,cpu主频是2GHz。

根据公式:

CoreMark / MHz = (CoreMark 分数) / (时钟频率,以兆赫兹为单位)

我们可以算出SG2042的 CoreMark / MHz=692303.531830/2000=346.55

从官网可以看到,截止目前(2023-8-16 )总共上传了767款型号的CoreMark跑分结果。

官网链接

https://www.eembc.org/coremark/scores.php

从排行榜上可以看到(上图1和图2),无论是基于 CoreMark 分数还是 CoreMark/MHz 分数,SG2042都展现出令人瞩目的表现。作为全球第一款 RISC-V 处理器芯片,它的分数已经值得充分的赞赏。尽管与第一名之间还存在一定的差距,但国产芯片将持续不断地努力,不断进步。让我们为国产芯片的未来发展加油!

正文完

-

About HS-2

HS-2 RISC-V通用主板是澎峰科技与合作伙伴共同研发的一款专为开发者设计的标准mATX主板,它预装了澎峰科技为RISC-V高性能服务器定制开发的软件包,包括各种标准bencmark、支持V扩展的GCC编译器、计算库、中间件以及多种典型服务器应用程序。

HS-2 RISC-V通用主板搭载了一颗国产RISC-V 64核处理器(SG2042)。SG2042是目前已量产的性能最高的RISC-V处理器,主要针对高性能计算领域需求设计,适用于科学计算、工程计算、AI计算、融合计算等大算力应用场景。

-

关于RISC-V公共测试平台

RISC-V高性能处理器公共测试云平台 ·快速使用指南,下载链接:https://www.kdocs.cn/l/cmnYcyFIlVRx

-

RISC-V公共测试云平台系列文章

-

RISC-V公测平台发布 ·Stream带宽完整测试

-

RISC-V公测平台发布 · 我的世界MohistMC

-

RISC-V公测平台发布 · 第一个WEB Server“Hello RISC-V world!”

-

RISC-V公测平台发布 ·如何在SG2042上玩转k3s

-

“RISC-V成长日记” blog发布,第一个运行在RISC-V服务器上的blog?

-

RISC-V公测平台发布:如何在SG2042上玩转OpenMPI

-

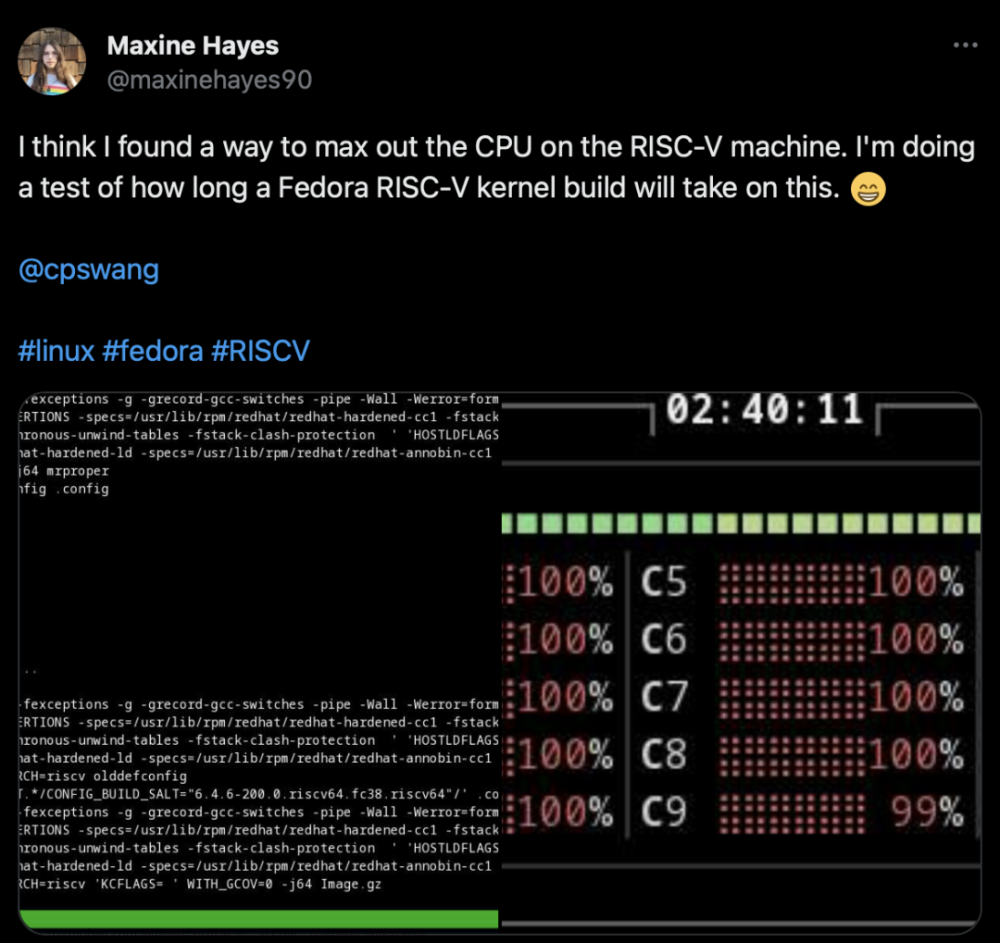

RISC-V公测平台发布:Compiling The Fedora Linux Kernel Natively on RISC-V

-

RISC-V公测平台发布 · Unix Bench完整测试

-

RISC-V公测平台发布 · 使用YCSB测试SG2042上的MySQL性能

-

RISC-V公测平台发布 · 7-zip 测试

-

RISC-V公测平台发布· CoreMark测试报告(本篇)文章来源:https://www.toymoban.com/news/detail-657763.html

欢迎投稿,发送至riscvinfo@perfxlab.com文章来源地址https://www.toymoban.com/news/detail-657763.html

到了这里,关于RISC-V公测平台发布· CoreMark测试报告的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[RISC-V]Milk-V开发板 i2c测试oled及波形输出](https://imgs.yssmx.com/Uploads/2024/02/520009-1.png)