前言

2023.8.15

一、锁存器

1、基本SR锁存器——或非门实现

信号高电平有效R:复位端S:置位端

表达式:Q = S + R' Qn

约束条件:SR=0,也就是SR不能同时为1

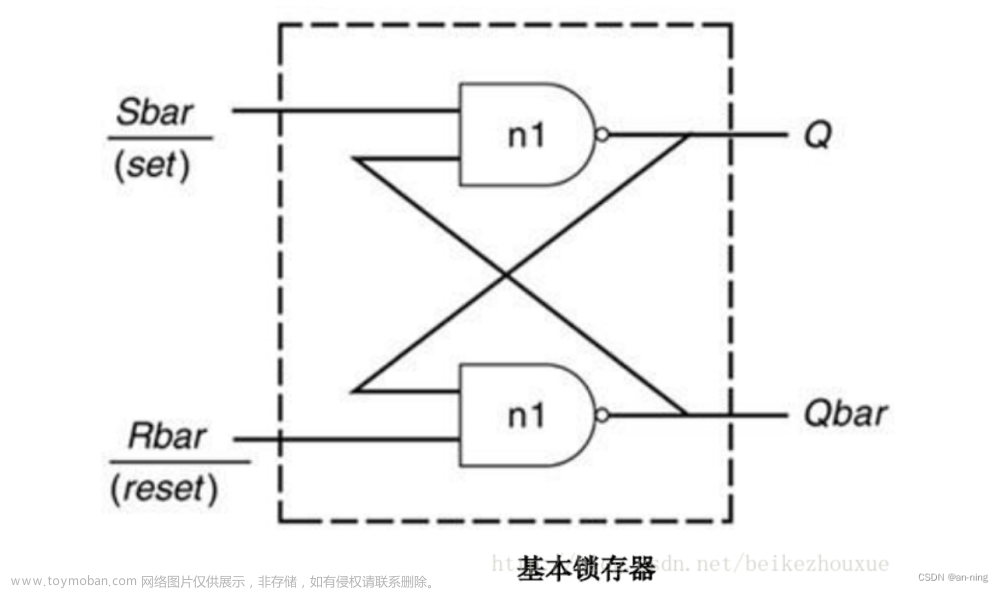

2、基本SR锁存器——与非门实现

信号低电平有效R:复位端S:置位端

表达式:Q = S' + R Qn

约束条件:S+R=1,也就是SR不能同时为0

3、门控SR锁存器

E = 0:锁存器保持不变,锁住E = 1:相当于正常得SR锁存器

4、门控D锁存器

把S取反接到R端

(4个与非门或者2个或非门+2个与门)

E = 0:锁存器保持不变,锁住E = 1:相当于正常得SR锁存器

二、触发器

1、 电平触发的RS触发器/同步SR触发器

把EN信号换成CLK即为电平触发的RS触发器clk=0:S=R=1,锁存器保持不变clk=1:表达式为Q = S + R' Qn

(clk=1的时候,相当于S和R接了非门再进入锁存器,所以之前与非门的时候是低电平有效,现在变成高电平有效了)

2、电平触发的D触发器/D型锁存器

clk=0:电路锁存clk=1:Q=D,且没有约束条件,因为输入是取反的,不可能同时为0或者同时为1

3、边沿触发的D触发器

主从结构实现clk=0:clk1=1,FF1锁存D输入的数据,FF2保持不变clk=1:clk1=0,FF1保持不变,FF2锁存数据输出

上面是上升沿有效触发

(如果要实现下降沿触发的话,只加一个反相器)

4、脉冲触发的RS触发器

clk=1:主触发器根据SR的状态进行翻转,从触发器不变clk由1变为0:主触发器不再改变,从触发器按照和主触发器相同的状态翻转

与非门构成的SR锁存器本是低电平有效,现在接了个与非门,变成高电平有效

约束条件:SR=0(也就是S、R不能同时为1)

5、主从JK触发器

- 主触发器clk高电平信号有效的话,翻转和置数发生在在下降沿

- 主触发器clk低电平信号有效的话,翻转和置数发生在在上升沿

| J | K | 功能 |

|---|---|---|

| 1 | 0 | 置1 |

| 0 | 1 | 置0 |

| 1 | 1 | 翻转 |

| 0 | 0 | 保持不变 |

上述题目,如果在高电平期间,有毛刺的话会对主触发器电路状态造成影响,因此主从结构最好还是分来画图,先画出主触发器的变化,再根据主触发器来判断从触发器。

三、D锁存器和D触发器的verilog实现

always@(posedge clk)

q <= d;

always@(*)

if(EN)

q <= d;

四、边沿触发、脉冲触发、电平触发的区别

电平触发:使能信号有效期间,数据输出随输入变化,这样会带来一些毛刺

- 电平触发的D触发器

- 电平触发的SR触发器

边沿触发:只在时钟上升沿或者下降沿数据有效,仅与该时刻的状态相关,能有效滤除掉毛刺文章来源:https://www.toymoban.com/news/detail-659805.html

- 边沿触发的D触发器(由两个电平触发的D触发器组成)

脉冲触发:一般是主从结构,主从触发器串联,触发信号反相

正脉冲:触发信号为高电平的时候,输入信号进入主触发器;触发信号为低电平的时候,主触发器不变,从触发器根据主触发器变化(因此信号只改变一次)文章来源地址https://www.toymoban.com/news/detail-659805.html

- 主从SR触发器

- 主从JK触发器

到了这里,关于verilog学习笔记6——锁存器和触发器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!