| author | daisy.skye的博客_CSDN博客-嵌入式,Qt,Linux领域博主 |

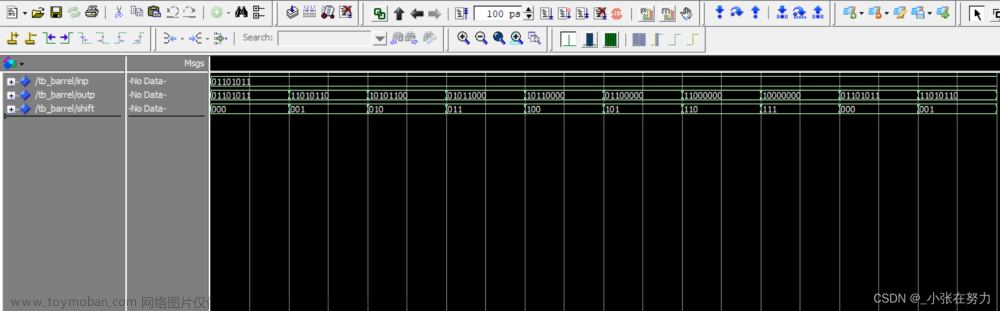

在使用移位符号用来当作除以号使用时,发现如下问题

其中 cnt_8K 为偶数和奇数时输出的数据不一样

reg [10:0] cnt_8K;

reg [10:0] ram1_addra;

always@(posedge clk_16M)

begin

if(ram_out_flag )begin

if(cnt_8K[0] == 1'd0)

ram1_addra <= cnt_8K >> 1 ;

else

ram1_addra <= cnt_8K >> 1 + 11'd128;//注意这里

end

end

但是在实际赋值过程如下代码的输出如下,其中当奇数时会一直输出0

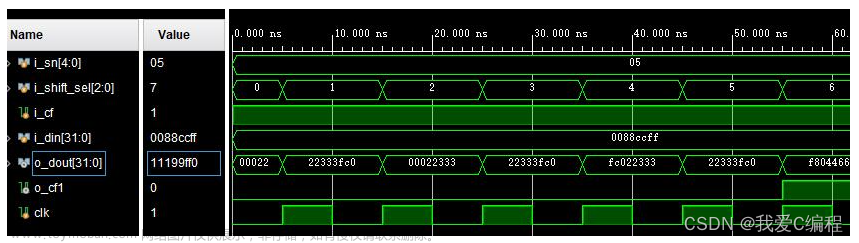

只需要修改添加括号后,输出就正常了文章来源:https://www.toymoban.com/news/detail-660635.html

//ram1_addra <= cnt_8K >> 1 + 11'd128;

ram1_addra <= (cnt_8K >> 1) + 11'd128;

文章来源地址https://www.toymoban.com/news/detail-660635.html

文章来源地址https://www.toymoban.com/news/detail-660635.html

到了这里,关于安路FPGA的赋值报错——移位处理,加括号的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!