VCS与Verdi联仿,简要工程模板,持续更新中…

一、背景

- 学习verilog,故用vcs来编译verilog,用verdi来查看波形。

- 提供一套简要verilog工程模板去执行教程中代码,并分析波形。

二、编写工程模块

- 建立工程在temp文件夹下新建文件夹/rtl、/sim、/tb,如下:

➜ CSDN cd temp

➜ temp ls

rtl sim tb

- 在/rtl文件夹下新建两个.v文件: template.v和timescale.v ,为模板rtl代码。

➜ rtl ls

template.v timescale.v

- 在/tb文件夹下新建.sv文件:tb_template.sv,为test bench文件。

➜ tb ls

tb_template.sv

- 在/sim文件夹下新建Makefile、runtemp和file.f文件,来进行vcs编译以及verdi看波形。

➜ sim ls

Makefile file.f runtemp

其中Makefile中的脚本为:

all:com verdi

com:

vcs -R -full64 +v2k -fsdb +define+FSDB -sverilog -f file.f -l run.log -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed

sim:

./simv -l sim.log

run_dve:

dve -vpd vcdplus.vpd &

clean:

rm -rf *.vpd csrc *.log *.key *.vdb sim* DVEfiles *.conf *.rc verdilog verdiLog

verdi:

verdi

其中Makefile为makefile脚本写的自动编译工具。runtemp为写的简易自动编译工具,主要给没有安装makefile或者gcc-4.8的环境,runtemp的内容是:

vcs -R -full64 +v2k -fsdb +define+FSDB -sverilog -f file.f -l run.log

#verdi

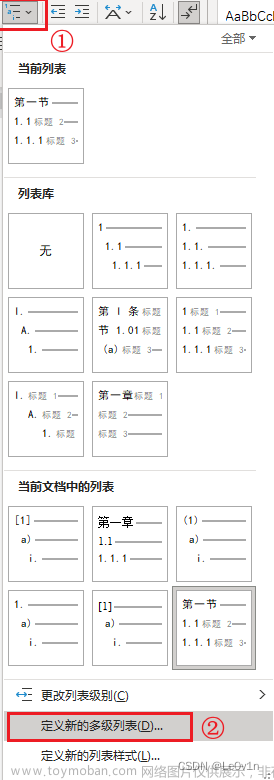

4.1 使用Makefile脚本来进行自动编译。

方法:在文件夹/sim下运行命令 make就会编译完成,并且生成波形文件,再用verdi查看即可。由vcs编译和verdi打开产生的文件可以用 make clean清除掉。

4.2 使用简易编译工具runtemp进行编译的命令为:source runtemp

至此,简要工程模板配置完成。

三、使用工程模板

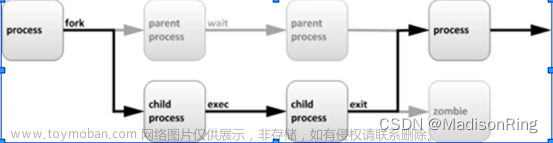

模板使用方法简要框图:

设计一个如下图的四选一选择器,用模板去编译和仿真看波形来验证模板是否正确。

- 选择器的rtl代码,把

mux4to1选择器的代码复制到模板的/rtl/template.v文件中:

module mux4to1(

input [1:0] sel ,

input [1:0] p0 ,

input [1:0] p1 ,

input [1:0] p2 ,

input [1:0] p3 ,

output [1:0] sout);

reg [1:0] sout_t ;

always @(*) begin

if (sel == 2'b00)

sout_t = p0 ;

else if (sel == 2'b01)

sout_t = p1 ;

else if (sel == 2'b10)

sout_t = p2 ;

else

sout_t = p3 ;

end

assign sout = sout_t ;

endmodule

- 四选一选择器的testbench代码,把其复制到模板的/tb/tb_template.sv文件中:

`timescale 1ns/1ps

module test ;

reg [1:0] sel ;

wire [1:0] sout ;

initial begin

sel = 0 ;

#20 sel = 3 ;

#20 sel = 1 ;

#20 sel = 0 ;

#20 sel = 2 ;

end

mux4to1 u_mux4to1 (

.sel (sel),

.p0 (2'b00), //path0 are assigned to 0

.p1 (2'b01), //path1 are assigned to 1

.p2 (2'b10), //path2 are assigned to 2

.p3 (2'b11), //path3 are assigned to 3

.sout (sout));

//finish the simulation

always begin

#100;

if ($time >= 1000) $finish ;

end

`ifdef FSDB

initial begin

$fsdbDumpfile("tb_template.fsdb");

$fsdbDumpvars;

end

`endif

endmodule

其中,每个自己的tb一定要保留如下片段,来保存仿真产生的信号波形,然后才能用verdi打开。

`ifdef FSDB

initial begin

$fsdbDumpfile("tb_template.fsdb");

$fsdbDumpvars;

end

`endif

接下来编译修改后的模板工程,打开文件夹/sim,在sim文件夹下输入make,在sim文件下产生这些文件:

其中,tb_template.fsdb文件就是verdi能打开的波形文件了。

然后通过下图中的步骤用verdi打开代码文件。

再按照如下步骤打开波形文件:

最后按如下步骤查看波形:

四、仿真结果

如下结果显示四选一选择器正确,故也得出模板工程正确。 文章来源:https://www.toymoban.com/news/detail-662041.html

文章来源:https://www.toymoban.com/news/detail-662041.html

五、工程下载地址

模板工程下载地址文章来源地址https://www.toymoban.com/news/detail-662041.html

到了这里,关于VCS与Verdi联仿,简要万能工程模板,持续更新中...的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!