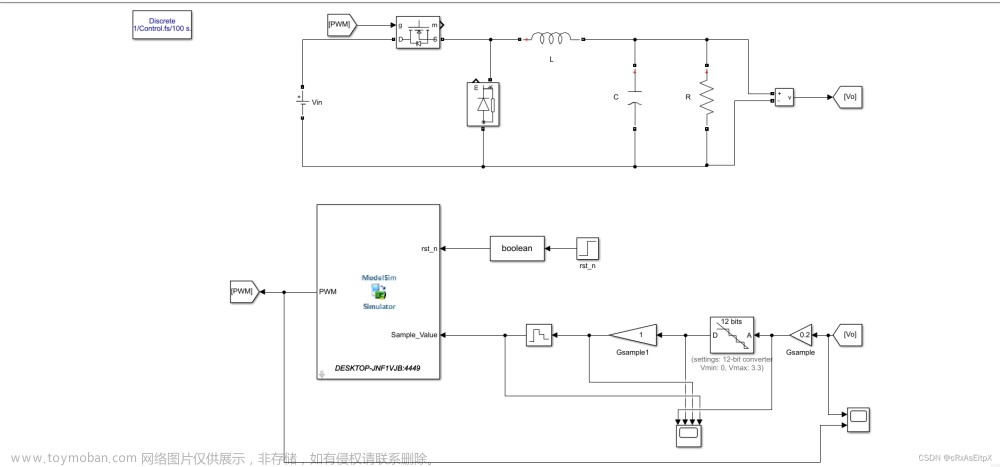

一、在modelsim中新建一个工程,然后写一个Verilog代码,然后编译,目的是为了得到此工程文件夹下的work文件。打开此工程的文件夹,找到work文件夹,复制到notepad++的安装路径下。

文章来源地址https://www.toymoban.com/news/detail-662332.html

(图1.是我自己在D盘创建的一个文件夹project_mux,用来存放步骤一modelsim生成的文件,图2.可以看到,这个work文件下有六个文件,它们是modelsim语法检查的工具)

(图3.是复制work文件到notepad++安装路径后的界面)

(图3.是复制work文件到notepad++安装路径后的界面)

二、安装插件NppExec

三、打开 NppExec插件,输入这段代码:cmd /k cd "$(CURRENT_DIRECTORY)" & vlog.exe "$(FULL_CURRENT_PATH)" & ECHO. & EXIT 然后save → 给这段代码取名 Run Verilog

→ ok

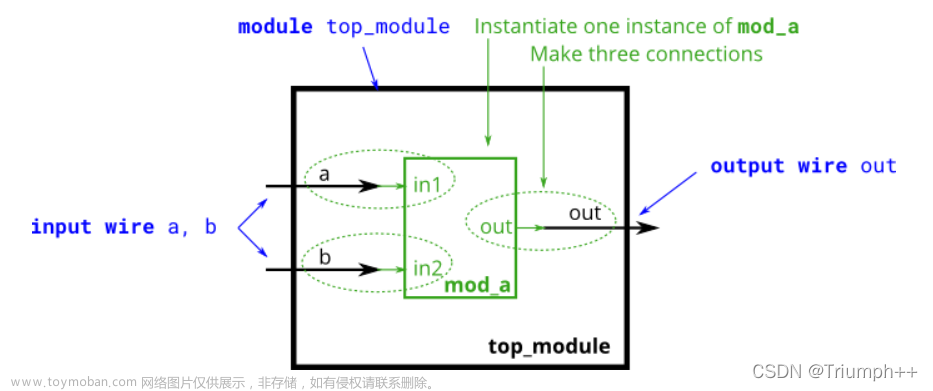

四、至此,notepad++的Verilog语法检查已经配置完成,可以在notepad++里试着写verilog 代码,

写完代码后,我们要进行保存。

点击保存(S)后,弹窗问你要保存在哪里,默认保存在notepad++的安装路径下

五、进行语法检查。

按Fn+F6键(有的电脑只按F6就可以了),然后便弹出我们之前的那段代码,点击ok,便开始语法检查。

(底下窗口是语法检查的报告,说明这段语法没有错)

(底下窗口是语法检查的报告,说明这段语法没有错)

六、为了进一步试试看它的检查效果,可以故意把之前第九行代码多加个分号。因为我们把代码改动了,所以又要进行保存,才能进行语法检查。

保存后,按Fn+F6键(有的电脑只按F6就可以了),然后便弹出我们之前的那段代码,点击ok

然后底下窗口出现新的语法检查报告,检查出第九行有错。

七、我们发现,每次修改代码后,都要重新点击保存,才能按Fn+F6键进行语法检查,这样有些麻烦。可以在NppExec插件中进行设置,把"save all file on execute" 它的意思是,在执行语法检查前保存文件。

勾选后,我们以后改了代码,Fn+F6便可直接执行语法检查,不用在语法检查之前按保存键了。

文章来源:https://www.toymoban.com/news/detail-662332.html

文章来源:https://www.toymoban.com/news/detail-662332.html

到了这里,关于notepad++的Verilog语法检查(调用modelsim的语法)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!