目录

一、前言

二、工程设计

2.1 工程代码

2.2 综合结果

2.3 仿真结果

一、前言

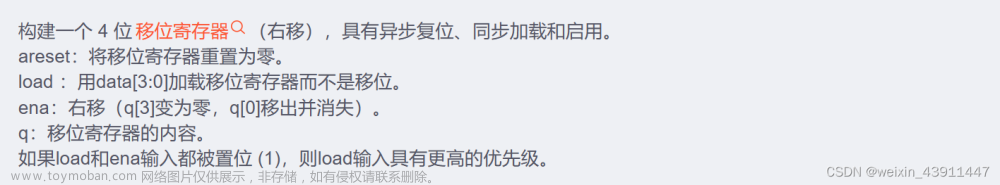

移位寄存器SRL在工程中属于使用频率较高个模块,可用于存储数据,实现串并转换;根据数据移动方向可分为左移寄存器,右移寄存器,左移是向数据高位移动,右移是向数据低位移动。

二、工程设计

2.1 工程代码

工程中包含了左移,右移,循环移位的设计,输出为8位。左移即输入不断从右边进入,同理,右移为输入不断从左边加入,循环移位此处为右循环,每一次变化都是第一位移到最高位,其他位都右移一位。

module SRL(clk,in,out_l,out_r,out_c,rst );

input clk,in,rst;

output reg [7:0] out_l,out_r,out_c=8'b00011001;

always@(posedge clk or negedge rst) //左移

begin

if(!rst)

out_l<=8'b0;

else

out_l<={out_l[6:0],in};

end

always@(posedge clk or negedge rst) //右移

begin

if(!rst)

out_r<=8'b0;

else

out_r<={in,out_r[7:1]};

end

always@(posedge clk or negedge rst) //循环移位

begin

if(!rst)

out_c<=8'b00011001;

else

begin

out_c[7]<=out_c[0];

out_c[6:0]<=out_c[7:1];

end

end

endmodule测试代码如下,使用系统random生成随机数作为输入

`timescale 1ns/1ps

module SRL_tb( );

reg clk,in,rst;

wire [7:0] out_l,out_r,out_c;

initial

begin

clk=0;

in=0;

rst=1;

#50 rst=0;

#100 rst=1;

end

always #1 clk=~clk;

always #2 in={$random}%(2); //每隔2秒随意生成一次0或1

SRL srl_test(.clk(clk),.in(in),.rst(rst),.out_l(out_l),.out_r(out_r),.out_c(out_c));

endmodule2.2 综合结果

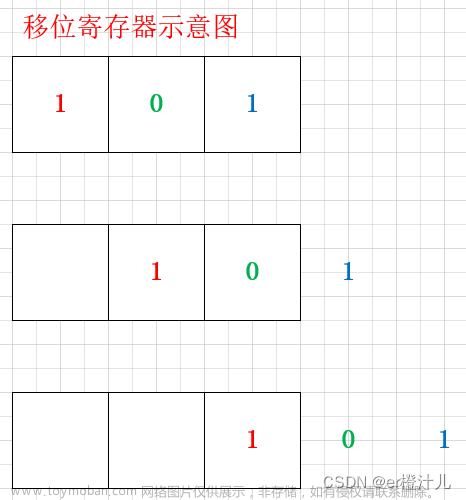

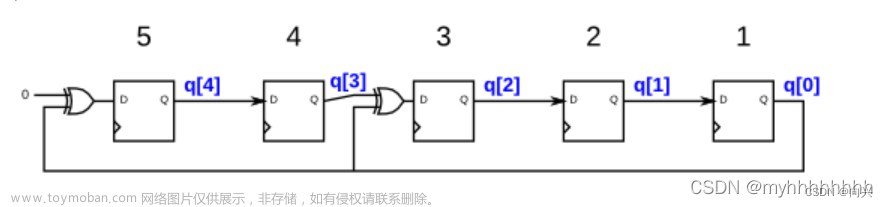

根据综合结果,左移和右移实现上为位置的对调,循环移位因为无需输入,故综合后只有输出

2.3 仿真结果

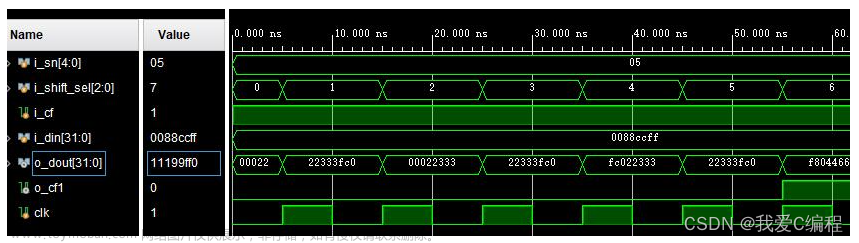

在红框1所在的时刻,输入in为0,out_l为10011111,out_r为11111001,out_c为10001100。在时钟clk的上升沿到来时,进行移位,左移out_l右边加0变为00111110,右移out_r左边加0变为01111100,out_c循环移位变为01000110。

红框2所在的时刻,输入in为1,在第二个时钟clk的上升沿到来时out_l变为01111101,out_r变为10111110,out_c循环移位变为00100011。符合预期文章来源:https://www.toymoban.com/news/detail-667141.html

文章来源地址https://www.toymoban.com/news/detail-667141.html

文章来源地址https://www.toymoban.com/news/detail-667141.html

到了这里,关于Verilog基础之十一、移位寄存器实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!