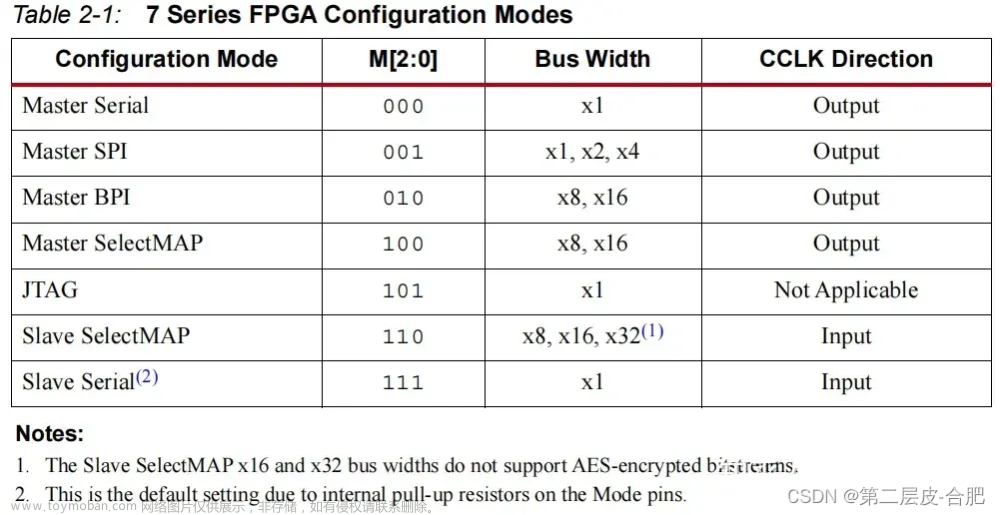

FPGA配置文件的下载模式有5种:

- 主串模式(master serial)

- 从串模式(slave serial)

- 主并模式(master selectMAP)

- 从并模式(slave selectMAP)

- JTAG模式

其中,JTAG模式在开发调试阶段使用。其余四种下载模式,可分为串行下载方式和并行下载方式。串行下载方式和并行下载方式都有主、从2种模式。

主、从模式的最大区别在于:主模式的下载同步时钟(CCLK)由FPGA提供;从模式的下载同步时钟(CCLK)由外部时钟源或者外部控制信号提供。

主模式对下载时序的要求比从模式严格得多,因此一般选择使用从串模式或从并模式。

一、从串模式

在从串模式下,加载FPGA程序需要使用的引脚:

CCLK: 加载时钟信号(输入),由控制器提供,上升沿有效;

PROGRAM_B: 加载模块的异步复位信号(输入),低电平有效,复位完成后变为高电平;

INIT_B: 初始化完成指示信号(输出),由低变高,表示FPGA初始化完成,低电平表示加载错误;

DONE: 加载完成指示信号(输出),高电平表示加载完成;

DIN: 串行配置数据线(输入);

M[2:0]: 模式选择管脚(输入),根据相应模式接外部上下拉电阻

此方式占用资源少,主要是和FPGA 相连的I/O接口较少;但一个配置时钟只能传输一个bit 数据,速度相对较低。

二、从并模式

在从并模式下,加载FPGA程序需要使用的引脚:

CCLK: 加载时钟信号(输入),由控制器提供,上升沿有效;

PROGRAM_B: 加载模块的异步复位信号(输入),低电平有效,复位完成后变为高电平;

INIT_B: 初始化完成指示信号(输出),由低变高,表示FPGA初始化完成,低电平表示加载错误;

DONE: 加载完成指示信号(输出),高电平表示加载完成;

D[8/16:0]: 加载数据线(输入),8位或者16位;

CSI_B: 片选使能信号(输入),低电平有效;

RDWR_B: 读写控制信号(输入),低电平为写,高电平为读;

M[2:0]: 模式选择管脚(输入),根据相应模式接外部上下拉电阻

并行加载端口与串行加载端口相比,多出如下信号线:

①、数据宽度由1增加到8/16位;

②、CSI_B(片选使能,输入);

③、RDWR_B(读写控制,输入);

从并加载接口占用的管脚资源较多,即使加载数据总线使用8位,也要14个管脚,CPU一般没有这么多通用输入/输出(GPIO)口,因此从并加载一般和CPLD配套使用。

CPU通过和CPLD的接口(8位的局部总线接口),将配置数据逐字节的写入CPLD的寄存器中。数据写入到CPLD后,再通过CPLD与FPGA之间的从并接口,将数据加载到FPGA。文章来源:https://www.toymoban.com/news/detail-667274.html

从并接口是同步总线,加载时间受限于总线时钟CCLK频率。理论上从并模式比从串模式运行速度快,但CPU写CPLD受限于写总线周期间隔,CPLD写FPGA受限于从并接口的时钟。文章来源地址https://www.toymoban.com/news/detail-667274.html

到了这里,关于FPGA配置文件从串并模式下载的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!