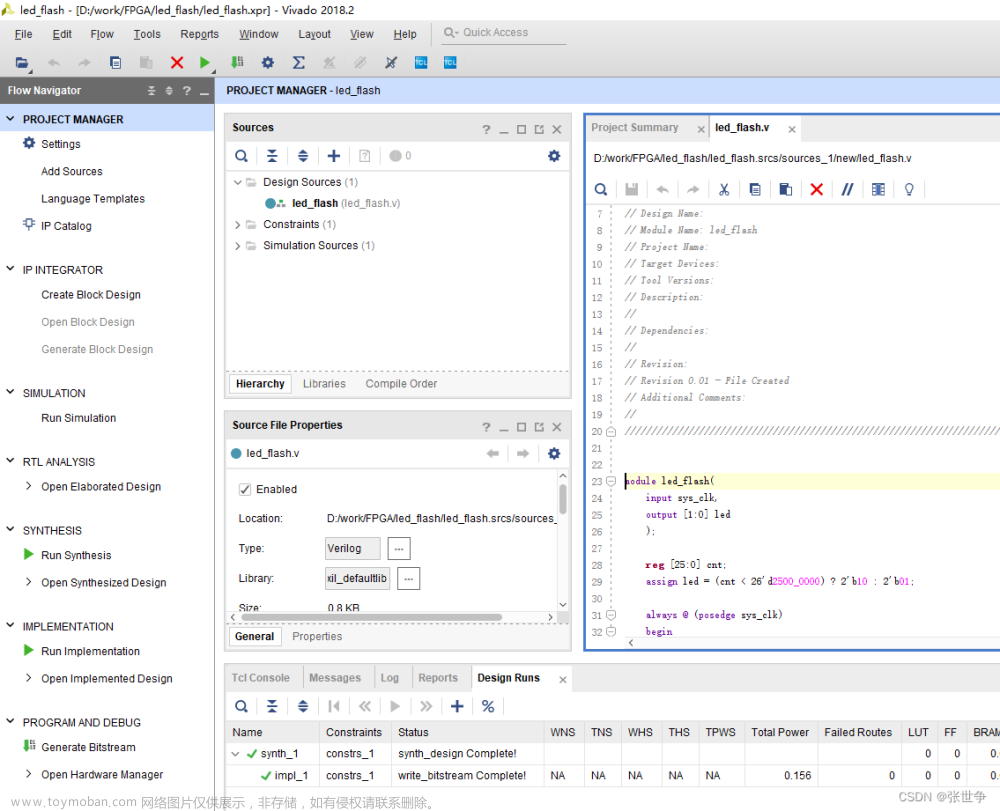

1.在project下的工程创建

#generate.tcl脚本中的目录可以自行更改

set device xc7z045

set package fbg676

set speed -1

set part $device$package$speed

set prjName xxxxx

set prjDir ./$prjName

set srcDir ./Source

create_project $prjName $prjDir -part $part

add_files [glob $srcDir/hdl/*.v]

add_files [glob $srcDir/hdl/*.vh]

add_files [glob $srcDir/ip/*.xcix]

updata_complie_order -fileset sources_1

addfiles -fileset constrs_1 [glob $srcDir/xdc/*.xdc]

addfiles -fileset sim_1 [glob $srcDir/tb/*.v]

updata_complie_order -fileset sim_1

set_property strategy Flow_AreaOptimized_high [get_runs srnth_1]

set_property strategy Performance_Explore [get_runs impl_1]

launch_runs synth_1

wait_on_run synth_1

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1

start_gui

#生成固化文件的方法

write_cfgmem -format mcs -interface SPIx4 -size 128 -loadbit {up 0x0 路径.bit} -file 路径.mcs

#如果你只是想创建工程文件,然后自己添加还没写的.v文件

set device xc7z045

set package fbg676

set speed -1

set part $device$package$speed

set prjName xxxxx

set prjDir ./$prjName

set srcDir ./Source

create_project $prjName $prjDir -part $part

file mkdir $prjDir/$prjName.srcs/sources_1/new

set fid [open $prjDir/$prjName..srcs/sources_1/new/xxx.v w]

close $fid

add_files $prjDir/$prjName.srcs.srcs/sources_1/new/xxx.v

#删除文件

file delete -force ddr_nn1.v

export_ip_user_files -of_objects [get_files F:/FPGA/DDRTEST/DDRTEST.srcs/sources_1/new/ddr_nn1.v] -no_script -reset -force -quiet

remove_files F:/FPGA/DDRTEST/DDRTEST.srcs/sources_1/new/ddr_nn1.v

2.钩子脚本

对于vivado的实现阶段有以下步骤

1.设计初始化阶段 init_design

2.设计优化 opt_design 默认执行

3.功耗优化 power_opt_design

4.布局 place_design 默认执行

5.布局后功耗优化 power_opt_design(post_place_power_opt_design)

6.布局后物理优化 phys_opt_design 默认执行

7.布线 route_design 默认执行

8.布线后物理优化 post_route_phys_opt_design

那么综合阶段的钩子脚本属性为

SET.SYNTH_DESIGN.TCL.PRE

SET.SYNTH_DESIGN.TCL.POST

实现阶段的钩子脚本属性有

SET.INIT_DESIGN.TCL.PRE

SET.INIT_DESIGN.TCL.POST

SET.OPY_DESIGN.TCL.PRE

SET.OPT_DESIGN.TCL.POST

可以发现,是实现阶段各个步骤的大写,所以就不一一展开书写

完整操作如下:

set_property SET.SYNTH_DESIGN.TCL.POST [get_files C:/report0.tcl -of [get_fileset utils_1]] [get_runs synth_1]

其中,get_files C:/report0.tcl -of [get_fileset utils_1]表示获取utils_1下的C:/report0.tcl文件

3.Non-Project模式

设计流程如下:

1.设置基本参数

2.读入设计源文件

3.对IP执行OOC综合操作

4.对整个设计进行综合操作

5.执行实现阶段的各个子步骤

6.生成位流文件

1设置基本参数

#与Prioject模式很相似 run_v1.tcl

set device xc7z045

set package fbg676

set speed -1

set part $device$package$speed

set top wave_gen

set srcDir ./Source

set SynOutputDir ./SynOutputDir

set ImplOutputDir ./ImplOutputDir

set synDirective Default

set optDirective Default

set placeDirective Default

set phys0ptDirectiveAp Default

set routeDirective Default

set phys0ptDirectiveAr Default

set_param general.maxThreads 6

source run_read_src_v1.tcl

source run_synth_ip_v1.tcl

source run_synth_v1.tcl

source run_impl_v1.tcl

source run_bitstream_v1.tcl

2.读入设计源文件

#run_read_src_v1.tcl

read_verilog [glob $srcDir/hdl/*.v]

read_verilog [glob $srcDir/hdl/*.vh]

read_edlf [glob $srcDir/netlist/*.edn]

read_ip [glob $srcDir/ip/*.xcix]

read_xdc [glob $srcDir/xdc/*.xdc]

link_design -top $top -part $part

3.对IP执行OOC综合操作

#run_synth_ip_v1.tcl

synth_ip [get_ips]

#synth_ip [get_ips chara-fifo]

#synth_ip [get_ips clk_core]

#表示只对指定IP进行ooc综合(out_of_context)

4.对整个设计进行综合操作

#run_synth_v1.tcl

synth_design -top $top -part $part -directive default

#top 指定顶层文件名 part指定FPGA型号 directive指定指令,这里是默认

write_checkpoint -force $SynOutputDir/post_synth

#这里创建了post_synth.dcp文件,并且覆盖了原有的post_synth.dcp文件

report_timing_summary -file $SynOutputDir/post_synth_timing_summary.rpt

report_utilization -file $SynOutputDir/post_synth_util.rpt

#生成了时序报告和资源利用率报告

5.执行实现阶段的各个子步骤

#run_impl_v1.tcl

#根据默认执行步骤,首先执行的是设计优化

opt_design -directive $optDirective

write_checkpoint -force $ImplOutputDir/post_opt

report_timing_summary -file $ImplOutputDir/post_opt_timing_summary.rpt

report_utilization -file $ImplOutputDir/post_opt_util.rpt

#然后是布局、布局后物理优化、布线,只需将上面的opt改为place phys_opt route即可,不一一写出

6.生成位流文件

#run_bitstream_v1.tcl

set_porperty CONFIG_MODE SPIx4 [current_design]

set_porperty BITSTREAM.CONFIG.CONFIGRATE 66 [current_design]

write_ bitstream -verbose -force -bin_file $ImplOutputDir/top.bit

#设置QSPI为四线模式,66MHz,同时生成.bin和.bit文件

7.将日志log文件保存到指定文件中

opt_design -directive Default > ./chech_opt.log

place_design -directive Default > ./chech_place.log

phys_design -directive Default > ./chech_phys.log

route_design -directive Default > ./chech_route.log

8.计算elapsed值

set start_time [clock format [clock seconds] -format "%s"]

place_design

set end_time [clock format [clock seconds] -format "%s"]

set place_elapse [clock format [expr $end_time - $start_time] -format "%H:%M:%S" -gmt true]

4.扫描策略

扫描策略是一种时序收敛方法。扫描策略分为扫描综合策略和扫描实现策略。在大多数情况下,扫描实现策略更为有效。

扫描实现策略实际上就是扫描不同的-directive值。

在Non-Project模式下,通常有5中扫描方式:文章来源:https://www.toymoban.com/news/detail-667874.html

模式0:只扫描place_design的-directive值(此时需要提供opt_design生成的.dcp)

模式1:只扫描route_design的-directive值(此时需要提供place_design生成的.dcp)

模式2:顺序扫描方式,即先提供place_design、phys_opt_design、route_design的-directive组合,然后进行扫描

模式3:先扫描place_design下的-directive值,从中获取WNS最好的情形,然后执行phys_opt_design,并在此基础上,扫描route_design的-directive值

模式4:交织扫描方式,即每一个place_design的-directive值和route_design的-directive值构成一个扫描对

获取WNS和WHS的命令:文章来源地址https://www.toymoban.com/news/detail-667874.html

set tps [get_timing_paths -max_paths 100 -setup]

set wns [get_property SLACK [lindex $tps 0]]

set tph [get_timing_paths -max_paths 100 -hold]

set whs [get_property SLACK [lindex $tph 0]]

到了这里,关于tcl学习之路(二)(vivado设计流程管理)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!