在PCB设计中,存在重复模块设计,如果重复绘制原理图和PCB将会耗费大量的精力,如果仅仅在PCB中使用特殊粘贴,创建的component和track又不具有网络(net)和对应的网表(netlist),不适用于我们检查错误。

在AD中,提供了对应的设计方法,分别对应原理图侧和PCB版图侧。

1、原理图设计

基本思想:将电路模块打包,并设置对外的接口。(自底向上设计)

比如现在想将某个原理图xxx.SchDoc,重新绘制12份。

1、绘制xxx.SchDoc,并设置port。具体方法:Place→Port。

2、新建顶层原理图:可以命名为xxx_TOP

在当前原理图下,点击Design >> create sheet symbol from sheet,弹出对话框如下:

选择后,点击OK,生成下方sheetsymbol

3、repeat 原理图,将这里从XXX_SingleDut 改为 Repeat(S,1,12)

repeat以后,得到如下原理图。

也就是说,C25的12 “胞妹”的名字分别叫:C25_S1、C25_S2… C25_S12.

为什么是S开头呢?因为repeat时是以S开头作为复制单元的designator.

具体可以参见在AD官网:链接: Creating a Multi-channel Design in Altium Designer

4、以总线的方式出线,如下:

1) 将对应的网络加上前缀repeat,例如:repeat(P3.3V)——意味每个子sheet的P3.3V单独为一个网络。可以观察到,GND网络并没有采用总线的方式出线,意味着12张sheet的GND接在一起,对应同一个net。

2) 用单根线将port网络引出

3) 放置Bus总线:Place→Bus

4) Bus总线命名规则:

那么对应单个网络的net以此为:P3.3V1、P3.3V2、P3.3V3… P3.3V12

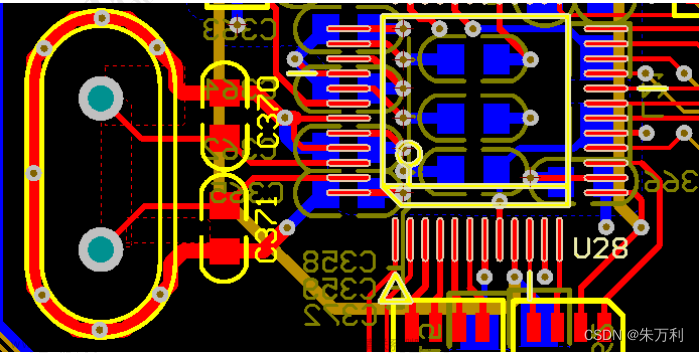

2、PCB 设计

1、将单个原理图对应的元件布局+连线

2、使用指令进行room排列:

A. Columns:横着摆的个数(列)

B. Rows:竖着摆的个数(行)

C. 注意修改X-spacing和 Y-spacing:指的是room和room的空隙间隔(room 的大小是可以调节的)

3、使用指令进行元件布局和Design » Rooms » Copy Room Formats »点击Source room »点击 Destination room

Room的copy可以选择 哪些room按照Source room进行copy

Option

a) Copy Component Placement:勾选代表——元件摆放相对位置一致

b) Copy Component Text Formats -:勾选代表——元件的designator和comment一致

c) Copy Routed Nets:勾选代表——走线layout一致

d) Copy Room Size/Shape:勾选代表——room的走线和尺寸一致

e) Copy Selected Objects Only:勾选代表——只有被选择的物体才被copy。

Touching Objects Options

a) Copy All Objects Touching the Room :勾选代表——只要接触到room的物体都可以被copy

b) Exclude NoNet Objects :勾选代表——没有net的物体不会被copy

Fully Enclosed Only/Enclosed & Touching

a) Fully Enclosed Objects Only:只有被room完全包裹的物体才会被复制

b) Enclosed & Touching Objects:全被被room包裹或者被room接触的都可以文章来源:https://www.toymoban.com/news/detail-669357.html

好啦,分享结束!有问题请留言~~文章来源地址https://www.toymoban.com/news/detail-669357.html

到了这里,关于Altium软件中相同模块布局布线的方法的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!