提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

我们在编译FPGA工程的时候一般需要对版本号的更新,一般来说都会有一个日期或者时间的版本标识,在上板调试的时候用于表征当前版本确实已经更新成功,或者作为FPGA发布版本的标识等等。但有时候我们有时候会忘记更新版本号,从而导致时间的浪费。

下面我们就是要解决这个痛点,利用vivado的tcl功能自动进行日期版本号的更新

创建.v文件

例如创建 一个version_date.v

里面就包含两句话 ,分别表示当前的年月日 和 时分秒

parameter [31:0] FPGA_VERSION_A = 32'h20221006 ;

parameter [31:0] FPGA_VERSION_B = 32'h000000 ;

在正式的工程文件,例如top.v中

assign AAA_reg = FPGA_VERSION_A;

assign BBB_reg = FPGA_VERSION_B;

设定tcl文件路径

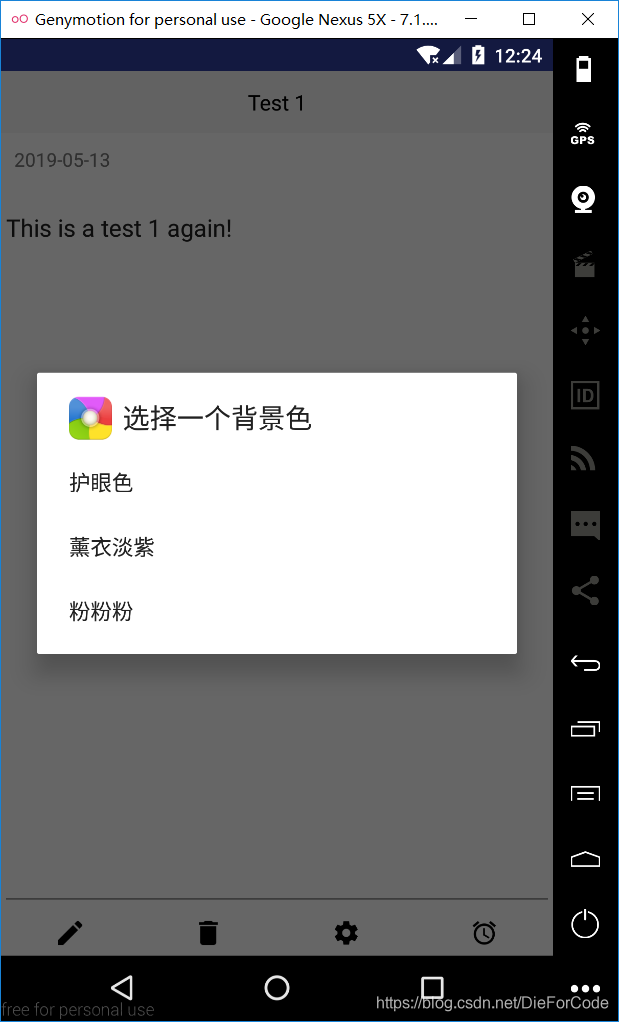

点击synthesis Settings

选中tcl的路径

tcl内容

set file_addr "../../version_date.v"

set time_now [clock seconds]

set time0 [clock format $time_now -format "%Y%m%d"]

set time1 [clock format $time_now -format "%H%M%S"]

set f [open $file_addr w]

set str "parameter [31:0] FPGA_VERSION_A = 32'h$time0 ;"

puts $f $str

set str "parameter [31:0] FPGA_VERSION_B = 32'h$time1 ;"

puts $f $str

close $f

注意tcl中的第一句话,因为 对于这个tcl而言 ,当前文件夹是 constrs_1 文件夹,而我们的version_date.v 放到了.xpr工程所在的路径中文章来源:https://www.toymoban.com/news/detail-669490.html

总结

这个小技巧解决了每次编译需要手动更新编译日期的问题。文章来源地址https://www.toymoban.com/news/detail-669490.html

到了这里,关于FPGA开发技巧备忘录——Vivado 自动日期版本号的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!