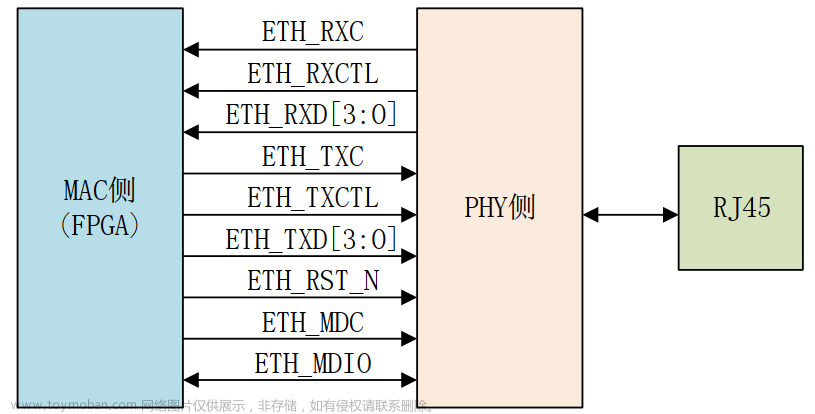

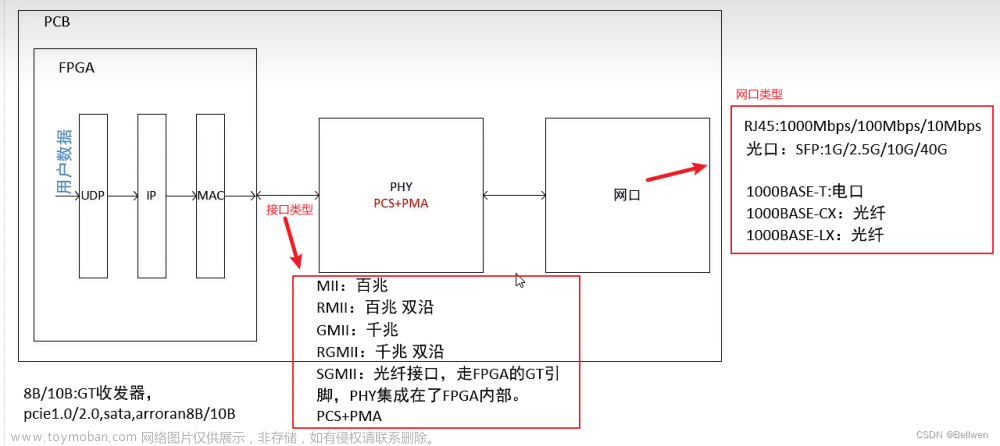

RGMII是以太网MAC连接PHY的一种接口,可以实现10/100/1000M网络速度,在FPGA系统中比较常见。RGMII在1000M模式下是双沿采样,而且要求采样端是center-aligned,所以其时序约束是比较复杂的。

下面分TX和RX来描述其时序约束应该怎么写。

TX:

通常的做法是使用ODDR实现双沿采样时序,如下图示。时序约束的重点是搞清楚有效的时序分析关系。对setup来说,分析上升沿到上升沿(RR),以及下降沿到下降沿(FF);对hold来说,分析上升沿到下降沿(RF),以及下降沿到上升沿(FR)。

TX的时序约束脚本:

##---------------------- TX ----------------------##

## clk_0 and clk_90 are derived clocks from PLL, so no need to re-define them.

## create a forward captrue clock

create_generated_clock -name rgmii_txc -source [get_pins ${rgmii_oddr_hier}u_ODDRE1_rgmii_txc/C] -multiply_by 1 [get_ports $src_rgmii_txc]

## TX: *_TXD and *_TX_CTL are synchronous to *_TXC, which is a dual-edge clock.

## Desired serup launch and capture relationship: RR and FF.

## Desired hold launch and capture relationship: RF and FR.

set_output_delay -clock rgmii_txc -max 1.0 [get_ports PAD_RGMII_TX_CTL]

set_output_delay -clock rgmii_txc -min -0.8 [get_ports PAD_RGMII_TX_CTL]

set_output_delay -clock rgmii_txc -max 1.0 [get_ports PAD_RGMII_TX_CTL] -clock_fall -add_delay

set_output_delay -clock rgmii_txc -min -0.8 [get_ports PAD_RGMII_TX_CTL] -clock_fall -add_delay

set_output_delay -clock rgmii_txc -max 1.0 [get_ports PAD_RGMII_TXD*]

set_output_delay -clock rgmii_txc -min -0.8 [get_ports PAD_RGMII_TXD*]

set_output_delay -clock rgmii_txc -max 1.0 [get_ports PAD_RGMII_TXD*] -clock_fall -add_delay

set_output_delay -clock rgmii_txc -min -0.8 [get_ports PAD_RGMII_TXD*] -clock_fall -add_delay

RX:

使用IDDR+一级FF做双沿采样,如下图示。对setup来说,分析上升沿到上升沿(RR),以及下降沿到下降沿(FF);对hold来说,分析上升沿到下降沿(RF),以及下降沿到上升沿(FR)。

RX的时序约束脚本:文章来源:https://www.toymoban.com/news/detail-670212.html

##---------------------- RX ----------------------##

## create a virtual launch clock outside of FPGA

create_clock -name vir_rgmii_rxc -period [expr $GMAC_RX_PERIOD]

## create capture clock on RXC PAD, which is +90 degrees shifted relative to launch clock

create_clock -name rgmii_rxc -period [expr $GMAC_RX_PERIOD] [get_ports $src_rgmii_rxc] -waveform {2 6}

## RX: *_RXD and *_RX_CTL are synchronous to *_RXC, which is a dual-edge clock.

## Desired setup launch and capture relationship: RR and FF.

## Desired hold launch and capture relationship: RF and FR.

set_input_delay -clock vir_rgmii_rxc -max 0.5 [get_ports PAD_RGMII_RX_CTL]

set_input_delay -clock vir_rgmii_rxc -min -0.5 [get_ports PAD_RGMII_RX_CTL]

set_input_delay -clock vir_rgmii_rxc -max 0.5 [get_ports PAD_RGMII_RX_CTL] -clock_fall -add_delay

set_input_delay -clock vir_rgmii_rxc -min -0.5 [get_ports PAD_RGMII_RX_CTL] -clock_fall -add_delay

set_input_delay -clock vir_rgmii_rxc -max 0.5 [get_ports PAD_RGMII_RXD*]

set_input_delay -clock vir_rgmii_rxc -min -0.5 [get_ports PAD_RGMII_RXD*]

set_input_delay -clock vir_rgmii_rxc -max 0.5 [get_ports PAD_RGMII_RXD*] -clock_fall -add_delay

set_input_delay -clock vir_rgmii_rxc -min -0.5 [get_ports PAD_RGMII_RXD*] -clock_fall -add_delay

set_false_path -rise_from [get_clocks vir_rgmii_rxc] -fall_to [get_clocks rgmii_rxc] -setup

set_false_path -fall_from [get_clocks vir_rgmii_rxc] -rise_to [get_clocks rgmii_rxc] -setup

set_false_path -rise_from [get_clocks vir_rgmii_rxc] -rise_to [get_clocks rgmii_rxc] -hold

set_false_path -fall_from [get_clocks vir_rgmii_rxc] -fall_to [get_clocks rgmii_rxc] -hold文章来源地址https://www.toymoban.com/news/detail-670212.html

到了这里,关于RGMII时序约束的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!