1 设计流程

均匀白噪声的产生我们使用m序列来生成并且把数据导出到matlab中观察其直方图。

2 FPGA实现14位的m序列

我们使用6个本原多项式,从而扩展14阶m序列的重复周期,原来是2^14-1,现在在原来的基础上周期扩大6倍。

2.1 产生14位的移位寄存器

//这次,我尝试使用6个本原多项式来扩展其周期

module ms14_generate

( data_1,

clk,

rst_n,

en,

ms14,

r14

);

//parameter INIT = 14'b0000_0000_0000_0001;

//data_1为m序列的初始值,从外部输入的,一般就设置为1

input wire [13:0]data_1;

input clk, rst_n;

input en;

output wire ms14;

output reg [13:0] r14;

// ms8 赋值为 r8信号的最地位

assign ms14 = r14[13];

reg r14_temp;

parameter cnt_MAX= 14'd16383;

reg [2:0]state;

reg [13:0] cnt0;

reg cnt0_flag;

wire clk_2;

always @ (posedge clk or negedge rst_n)begin

if(!rst_n)

r14 <= data_1;

else if(en) begin

r14[0] <= r14[1];

r14[1] <= r14[2];

r14[2] <= r14[3];

r14[3] <= r14[4];

r14[4] <= r14[5];

r14[5] <= r14[6];

r14[6] <= r14[7];

r14[7] <= r14[8];

r14[8] <= r14[9];

r14[9] <= r14[10];

r14[10] <= r14[11];

r14[11] <= r14[12];

r14[12] <= r14[13];

r14[13] <= r14_temp;

end

else

r14 <= r14;

end

2.2 切换不同的本原多项式

//由于14阶的m序列周期为16384,所以每隔16384个计数值,

//状态变一次,对应m序列的第14位赋不同的值。

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt0 <=14'd0;

else

cnt0 <= cnt0+1'b1;

always@(posedge clk or negedge rst_n)

if(!rst_n)

state <=3'd0;

else if(state == 3'd5 && cnt0 ==cnt_MAX-1)

state <=3'd0;

else if(cnt0 ==cnt_MAX-1)

state <= state+1'b1;

//这里是在matlab命令行里面输入一个函数,就可以显示14阶的所有本原多项式

//具体函数可以百度

//下面的规律就是r14[x]里面的x要和D^y中y,两者加起来为14

//你可以在'd0那几行验证一下。

/*

D^14+D^13+D^10+D^4+D^2+D^1+1

D^14+D^13+D^12+D^10+D^4+D^1+1

D^14+D^13+D^10+D^6+D^2+D^1+1

D^14+D^13+D^12+D^8+D^4+D^1+1

D^14+D^12+D^10+D^1+1

D^14+D^13+D^4+D^2+1

*/

always@(posedge clk or negedge rst_n)

if(!rst_n)

r14_temp<=1'b0;

else case(state)

'd0: r14_temp <= r14[0]^r14[1]^r14[4]^r14[10]^r14[12]^r14[13];

'd1: r14_temp <= r14[0]^r14[1]^r14[2]^r14[4]^r14[10]^r14[13];

'd2: r14_temp <= r14[0]^r14[2]^r14[4]^r14[13];

'd3: r14_temp <= r14[0]^r14[1]^r14[4]^r14[8]^r14[12]^r14[13];

'd4: r14_temp <= r14[0]^r14[1]^r14[10]^r14[12];

'd5: r14_temp <= r14[0]^r14[1]^r14[2]^r14[6]^r14[10]^r14[13];

default:r14_temp <= r14[0]^r14[1]^r14[4]^r14[10]^r14[12]^r14[13];

endcase

endmodule

3 modelism仿真,并把数据写入到TXT文件

3.1 verilog代码

`timescale 1ns/1ns

module ms14_generate_tb ();

reg clk, rst_n;

reg [31:0] seed_val;

integer fd;

wire [7:0] r14;

wire ms14;

reg reseed;

ms14_generate ms14_generate

(

.clk(clk),

.rst_n(rst_n),

.en(1),

.ms14(ms14),

.r14(r14)

);

initial begin

clk = 0;

rst_n =0;

#20

rst_n =1;

end

always #10 clk <=~clk;

initial begin

#1000

//延迟一段时间,再写入txt文件里面

reseed = 0;

seed_val = 32'd1234;

//上面两个我也不知道啥意思,直接用就好了

fd = $fopen ( "random.txt" , "w" ) ;

#10 reseed = 1;

#10 reseed = 0;

#10000000 ;

$fclose ( fd ) ;

$stop;

end

reg delay;

initial begin

delay = 0;

#400

delay = 1;

end

always @(posedge clk_10M) begin

if(delay)

$fwrite (fd,"%d\n",$signed(r14));

//$fwrite (fd,"%d\n",(r14));

end

endmodule //tb_gauss_noise

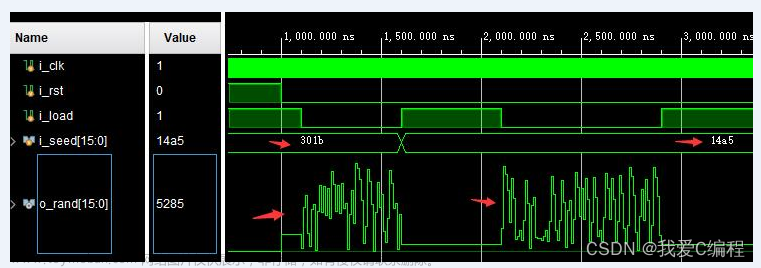

3.2仿真结果

好,均匀噪声就生成了,不过我们最好还是导入到matlab中看看其结果文章来源:https://www.toymoban.com/news/detail-671438.html

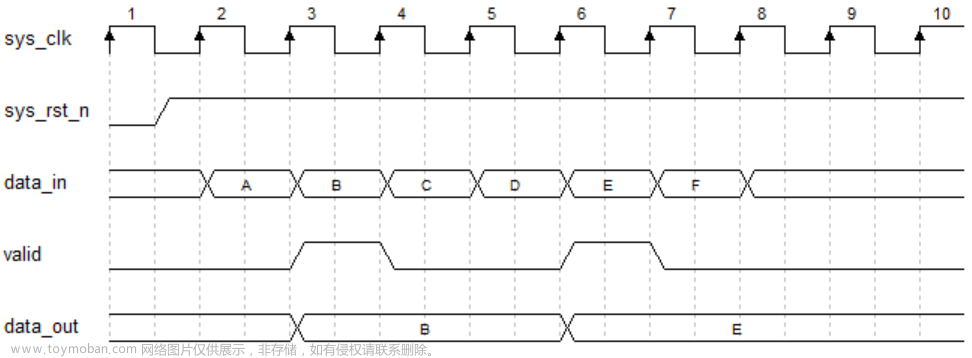

3.3噪声直方图

好!设计实现了!!!文章来源地址https://www.toymoban.com/news/detail-671438.html

到了这里,关于基于FPGA的均匀白噪声的产生的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!