首先,要先了解几个概念:

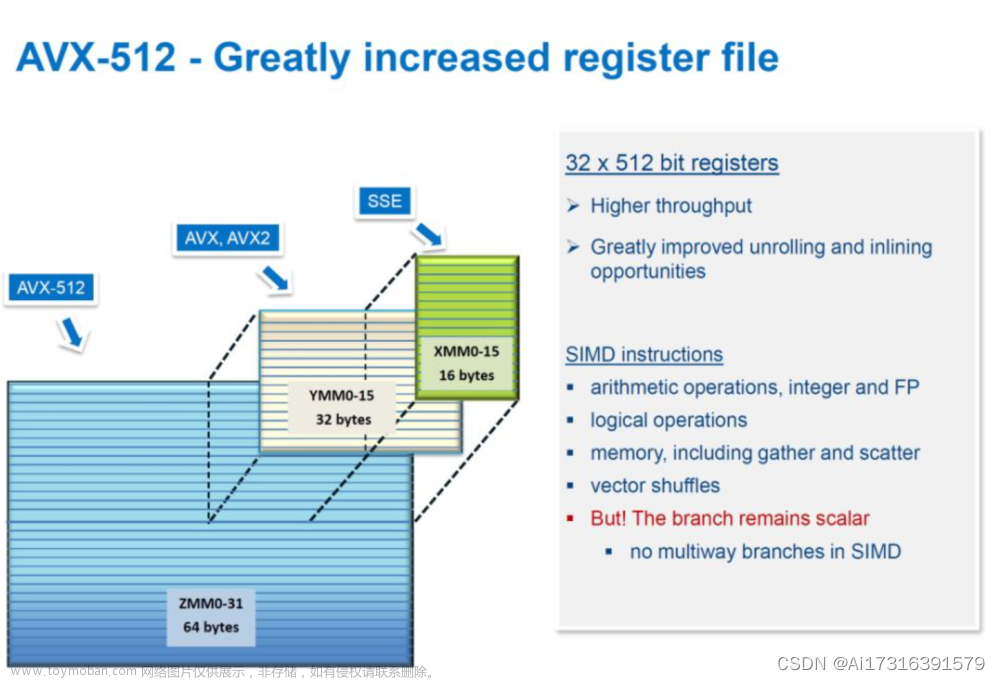

1、线程是CPU调度和分配的基本单位。

2、进程是操作系统进行资源分配(包括cpu、内存、磁盘IO等)的最小单位 。

3、一个进程可以包括多个线程。

4、CPU的时间片是由计算机的操作系统OS里的调度器分配的. 当多个线程需要执行时,OS里的调度器会将CPU的执行时间划分为多个小的时间片,并依次分配给每个线程。

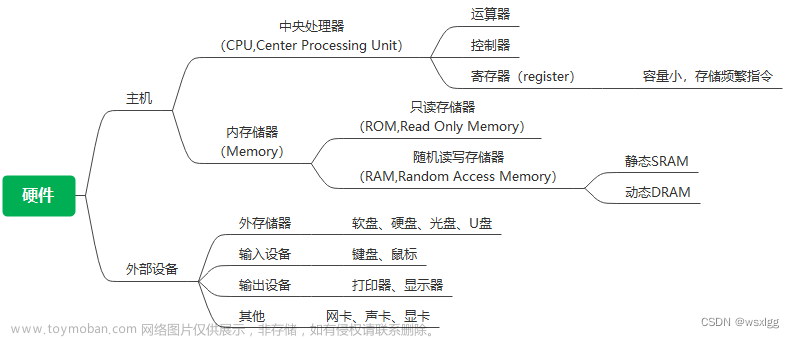

5、操作系统内存管理模块:管理物理内存、虚拟内存相关的事务。

并行和并发

并发:在同一个核心的CPU中,同一个时刻,只能有一条指令执行,但多个线程上下文的指令被快速轮换执行,使得在宏观上具有多个进程同时执行的效果

并行:是指在同一个时刻,多个核心上不同的线程指令同时执行。

单核cpu多线程有必要吗?

通常一个任务不光 cpu 上要花时间, io 上也要花时间(例如去数据库查数据,去抓网页,读写文件等)。 一个进程在等 io 的时候, cpu 是闲置的,另一个进程正好可以利用 cpu 进行计算。 多几个进程一起跑,可以把 io 和 cpu 都跑满了。

也就是说,充分发挥单核CPU的性能,就要创建足够多线程来填满单核CPU上的时间片。但并非线程越多越好,由于线程之间存在竞争、上下文切换时的开销。

时间片

时间片代表了CPU分配给每个线程的最小时间单位。在多任务的OS中,当多个线程或进程需要执行时,计算机的操作系统OS里的调度器会将CPU的执行时间划分为多个小的时间片,并依次分配给每个线程或进程。

时间片的长度由系统内核、调度算法来决定的,可以是几毫秒或几十毫秒的量级。

上下文切换

切换过程:

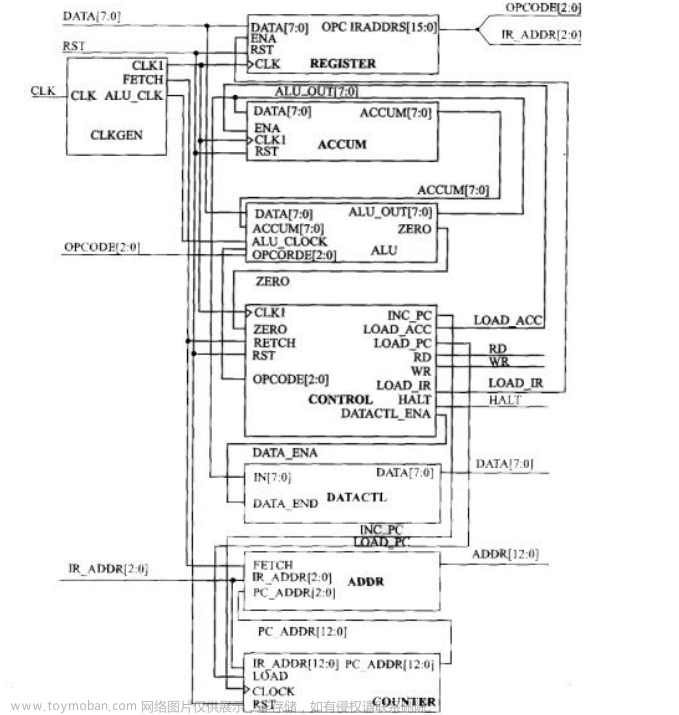

1.A线程的时间片用完后,操作系统会剥夺该线程的CPU执行权,CPU会将A线程此刻用的数据存到寄存器中,将执行到哪一步的信息存到程序计数器中.

2.这时,轮到B线程开始执行了, CPU去处理B线程, 当B线程的时间片用完后,又会和线程A一样被暂时封存起来.

3.线程A解封,CPU又开始执行线程A.

时间片+上下文切换的优缺点

优点:

1.充分利用cpu的效率

2.不同线程进行时间片轮转调度,实现了多个任务的并发执行效果。

缺点:文章来源:https://www.toymoban.com/news/detail-671446.html

增加线程上下文切换给cpu带来的额外的性能开销。文章来源地址https://www.toymoban.com/news/detail-671446.html

到了这里,关于单核cpu是怎么处理多线程的的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!