目录

一、简介

二、测试访问端口

2.1 端口说明

2.2 TAP 控制器

2.3 指令、数据寄存器

三、边界扫描结构

3.1 结构概览

3.2 BSR基本结构类型

3.3 EXTEST指令

四、多TAP扫描链

一、简介

1149.1协议定义了可包含在集成电路中的测试逻辑,以提供标准化的方法,其主要包含以下两点:

1.测试板级(PCB)或其他基层上的不同芯片间的互联;

2.测试芯片内部自身逻辑,可用于控制信号,也可用于观测信号。

如下图所示,1149.1测试逻辑主要由边界扫描寄存器(boundary-scan register,BSR)、其他内建的控制或观测寄存器(Test Data Register,TDR)组成,并通过测试访问端口(Test Access Port,TAP)访问。JTAG内部逻辑寄存器的访问一般由两步组成:1.选择指令寄存器(选择地址);2.指令寄存器使能后即选中了对应的数据寄存器。此外,一般BSR,IDCODE,BYPASS是必须的,TDR是可选的(根据用户需求定义)。

二、测试访问端口

2.1 端口说明

JTAG信号引脚一共有4个或者5个(其中一个可选)。这些引脚仅用于测试目的,控制JTAG完成1149.1协议的操作。引脚信息如下:

Test clock input(TCK):该引脚为测试逻辑提供时钟,由于受板级以及芯片pad限制,一般频率为10MHz,频率占空比一般为50%。

Test mode select input(TMS):用于控制JTAG内部状态机跳转,切换到指定,该信号在TCK上升沿时被采样。

Test data input(TDI):串行输入指令/数据,该信号在TCK上升沿时被采样。

Test data output(TDO):串行输出指令/数据,该信号在TCK下降沿时被采样输出,外部指令以及数据在TDI和TDO之间传输。

Test reset input(TRST*):JTAG 内部逻辑全局异步复位信号,一般低电平有效。该信号时可选信号,原因是可以通过TMS shift 5拍1使状态机处于Test-Logic-Reset状态,也可以复位内部逻辑,所以不一定需要该信号。

2.2 TAP 控制器

如下图所示,所有的JTAG操作的源头都是由一个具有16个状态的同步状态机控制的。该控制器使用TCK为时钟,使用TMS为其输入,如果需要复位时使用TRSTN。状态的跳转是由TMS输入1或者0决定的。状态机分为如下两列,左边绿色的是控制数据寄存器,右边蓝色的是控制指令寄存器。

常用状态:

Test-Logic-Reset : 控制器的第一个状态是复位状态。通过发出TRSTN或者在五个连续时钟内一直把TMS置为1可进入这种状态。在这种状态下,一个复位信号会被发送到所有寄存器组件,以将其重设为它们的初始状态。

Run-Test/Idle:如果TMS为0,TAP控制器能进入的下一个状态是Idle状态,即空闲状态。当TMS为1时,退出该状态并进入下一个状态。IR状态走完进入DR状态时,可以走Run-Test/Idle状态,也可以不走。

Select-DR-Scan/Select-IR-Scan:该状态是一个暂时状态。

Capture-DR/Capture-IR:在该状态下,系统会发出指令寄存器ClockDR/ClockIR,并使其执行捕获操作。

Shift-DR/Shift-IR:在该状态下,数据寄存器以及指令寄存器会被置于TDI和TDO之间,并且时钟上升沿时进行串行移位,TDO只在该状态下有效,其他状态TDO为High-Z。

Update-DR/Update-IR:在该状态下,系统会更新对应的指令寄存器或数据寄存器。

2.3 指令、数据寄存器

如下图所示,一般指令寄存器结构。当TAP状态处于Capture-IR时,系统发出CaptureEn信号,将Din信号捕获进Capture寄存器。当TAP处于Shift-IR时,系统发出ShiftEn信号,SI到SO通路被打通,可以进行移位操作。当TAP处于Update-IR时,系统发出UpdateIR信号,Update寄存器值更新到Capture 寄存器出输出值。

指令寄存器的长度最短位2,目前业界一般使用4位或者8位。常用的指令寄存器如下

(以8位IR宽度举例):

BYPASS:一般指令为8‘hFF

IDCODE: 一般指令为8’h01,指明器件可识别ID

EXTEST:外测试指令,BSD指令集

INTEST:内测试指令,BSD指令集

PROLOAD:预加载指令,BSD指令集

等等。

数据寄存器结构类似于上面的指令寄存器,在这里就不重复描述了。除了上述描述的指令对应的数据寄存器外,还有可用户自定义的寄存器。

三、边界扫描结构

3.1 结构概览

如下图所示,在芯片pad和内核逻辑之间插入BSR寄存器实现PAD可控测试目的。当BSR指令被选中时,data可以从TDI shift进8个BSR中,并从TDO口依次shift出对应的值。

3.2 BSR基本结构类型

最基本的BSR类型是BC_4,只有1个mux和1个寄存器,不过它的使用也很局限,只可以用作观测信号,不可作为控制信号。

实用性更高的cell如BC_1 cell,可用于观测也可用于控制。 支持capture、shift、update功能,可用于输入或输出BSR cells。

BC_2和BC_1有点类似,不同的是两个cell capture的行为不一样,BC_1捕获的是data_in的值,而BC_2捕获的是update寄存器。

BC_7最为复杂,支持双向port。

四、多TAP扫描链

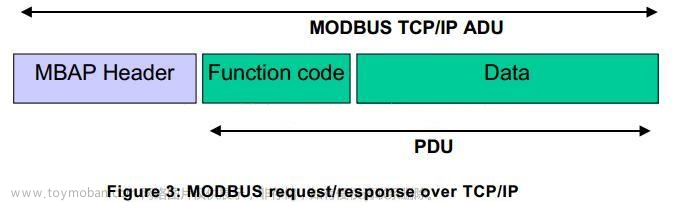

如下图所示,当前芯片设计中一般有多组TAP,多组TAP的解决方案有如下几种方式:

1.第一种多个TAP相互独立,互不干扰,但是需要分别拉信号到PAD,这种方式浪费pad资源,一般很少用;

2.第二种方案如下图所示,将所有的TAP 串联起来,TDI进TDO出,中间的TAP TDI/TDO首尾相接,其他信号TMS/TCK/TRSTN 共享。这样的好处是只用一组JTAG 引脚可以访问芯片内所有TAP。使用时,如果只操作其中一个TAP,其他TAP处于bypass状态,读到这里是否注意到这种方式的缺点:操作不同的TAP需要计算其他TAP BYAPSS占用的1bit,对于读出的数据不太友好,当然也可以通过软件处理得到想要的数据。

文章来源:https://www.toymoban.com/news/detail-672389.html

文章来源:https://www.toymoban.com/news/detail-672389.html

3.第三种多个TAP用1到2组PAD控制,可以onehot控制,这涉及到TAP间如何切换,后续有空讲解这部分。文章来源地址https://www.toymoban.com/news/detail-672389.html

到了这里,关于【JTAG】1149.1协议详解的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!