基于ZYNQ FPGA的8路ADC数据采集与存储实现

概述:

在工程设计和科学研究中,数据采集与存储是一个重要的任务。为了满足高速、高精度和大容量的数据采集需求,本文将介绍如何基于ZYNQ FPGA平台实现8路ADC数据采集与存储。通过合理的硬件设计和软件开发,我们可以实现快速而稳定的数据采集与存储系统。

硬件设计:

- ADC选择:选择8路合适的ADC进行模数转换,以满足采集的需求。可以考虑采用带有SPI或者I2C接口的ADC芯片。

- ZYNQ FPGA:选择一款具备强大的计算和数据处理能力的ZYNQ系列FPGA作为主控芯片。这种FPGA内部集成了ARM处理器和可编程逻辑单元,能够满足高速数据传输和处理的要求。

- 时钟和触发信号:设计合适的时钟和触发信号源,确保数据采集的同步性和精度。

软件开发:文章来源:https://www.toymoban.com/news/detail-675353.html

- FPGA逻辑设计:使用HDL(硬件描述语言)如Verilog或VHDL来描述FPGA的逻辑电路。根据采样率和数据精度的要求,设计适合的数据通路和控制逻辑。

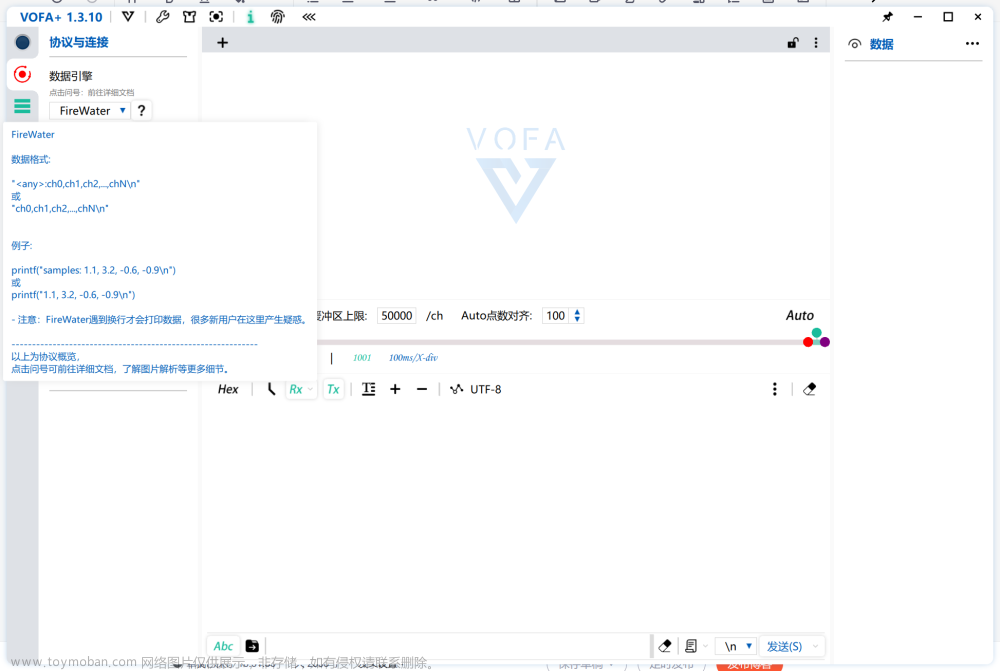

- 嵌入式软件开发:使用嵌入式C/C++编程语言,结合FPGA提供的开发工具和API,进行软件开发。实现与FPGA的通信、触发控制、数据缓存等功能。

数据采集与存储流程:文章来源地址https://www.toymoban.com/news/detail-675353.html

- 初始化:设置ADC参数、配置FPGA逻辑电路和初始化存储设备。

- 数据采集:根据触发信号和时钟控制,FPGA逻辑电路将ADC的输出进行采样,并将数据传输给FPGA内部的缓存。

- 数据处理:FPGA内部的数据缓存将数据进行处理,如滤波、采样率转换等。也可以在嵌入式软件中对数据进行实时处理。

- 数据存储:将处

到了这里,关于基于ZYNQ FPGA的8路ADC数据采集与存储实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!