1. FPGA入门

- 快速上手verilog语法

- 状态机,线性序列机

- FPGA常见的设计方法

- 自己写代码,下载代码进行使用,使用厂家/第三方提供的IP核

- 常见接口设计

等等。。

学习时间:基础内容的学习 - 20*8h,啊啊啊我可以我能行,看来这个月我给把时间砸这上面了~~

仿真两大作用:检查验证设计功能是否正确;调试问题,可以看到设计中每一个信号每一个时刻的值,通过仿真分析设计中信号异常的原因。做设计时,超过50%的时间不是在写代码,而是通过仿真调试代码找问题。

2. FPGA开发流程

写一套硬件描述语言,能够在指定硬件平台实现相应功能。

- 设计定义:比如让LED灯1s闪烁一次

- 设计输入: 编写逻辑(使用verilog代码描述逻辑);画逻辑图;使用IP

- 分析综合 (由专业的EDA软件进行,Quatus、vivado、ISE):对所写的逻辑描述内容进行分析,并得到逻辑门级别的电路内容

- 功能仿真:使用专门的仿真工具进行仿真(Modelism),对于数字电路来说,方针是基本接近于真实情况的。

- 布局布线:(vivado、quartus)在指定器件上将设计的逻辑电路实现

-

分析性能

- 时序仿真(非常耗费时间)

- 静态时序分析

- 下载到目标板上运行调试,查看结果ILA

让设计的逻辑在目标板上正常工作 - 功能正常、性能稳定

3. 二选一多路器 - 快速熟悉开发环境及流程

快速熟悉环境及流程

1. 编码

module mux2( //端口列表

a,

b,

sel,

out

);

//端口定义

input a;

input b;

input sel;

output out;

//2 select one

assign out = (sel==1)?a:b;

endmodule

2. 分析综合

3. 功能仿真

添加激励文件 text bench

`timescale 1ns/1ns

module mux2_tb(); //without port

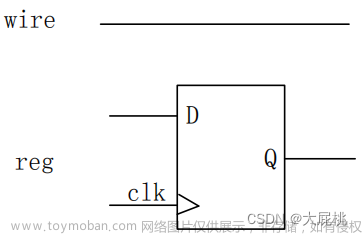

reg s_a; //激励信号

reg s_b;

reg sel;

wire out;

//例化- 复制过来,稍微改动

mux2 mux2_inst0(

.a(s_a),

.b(s_b),

.sel(sel),

.out(out) //连信号线

);

//initial块 - 变化高低电平

initial begin

s_a = 0; s_b = 0; sel = 0;

#200; //延迟200,注意这只适用于描述激励

s_a = 0; s_b = 0; sel = 1;

#200;

s_a = 0; s_b = 0; sel = 0;

#200;

s_a = 0; s_b = 1; sel = 1;

#200;

s_a = 1; s_b = 1; sel = 0;

#200;

s_a = 1; s_b = 0; sel = 1;

#200;

s_a = 1; s_b = 1; sel = 0;

#200;

s_a = 1; s_b = 1; sel = 1;

#200;

$stop;

end

endmodule

- 1ns/1ps:时间单位/精度

-

initial块

4. 布局布线 run implementation

5.时序仿真

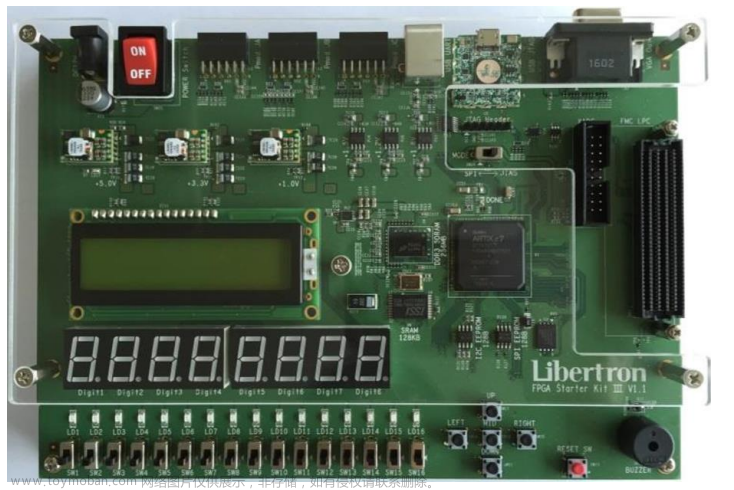

6. 下载到板子上,调试

分配IO引脚

ctrl+s

我艹,之前我都是照猫画虎自己胡写的。。。

7. 生成比特流文件

- Generate Bitstream

- Open Hardware Manager - 要先上电哦

啊哈哈好好玩啊,当然被自己笨拙的样子笑到

open target → auto connect文章来源:https://www.toymoban.com/news/detail-676413.html

Program device 就ok啦~文章来源地址https://www.toymoban.com/news/detail-676413.html

到了这里,关于【FPGA】FPGA入门 —— 基本开发流程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!