在开始测试过程之前,必须要了解某些测试的概念,理解这些概念,才能为了设计确定最好的测试方案

扫描电路有助于测试生产,并且能够减少外部测试仪的使用,这里有两种主要类型的扫描电路:internal scan和boundary scan。internal scan也被称为scan design是在内部改进设计的电路来提高电路的可测试性。

扫描设计修改了初始设计中的电路,而边界扫描在设计的外围增加了扫描电路,使芯片上的内部电路通过标准版接口可访问,增加的电路增强了芯片、芯片I/O pads以及芯片与其他电路板的互连的电路板可测试性。

Scan Design Overview

internal scan或者scan design是一个设计电路的内部改进为了增加设计的可测试性。

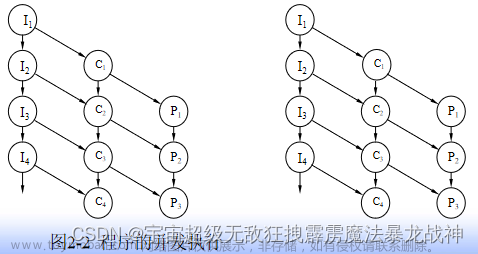

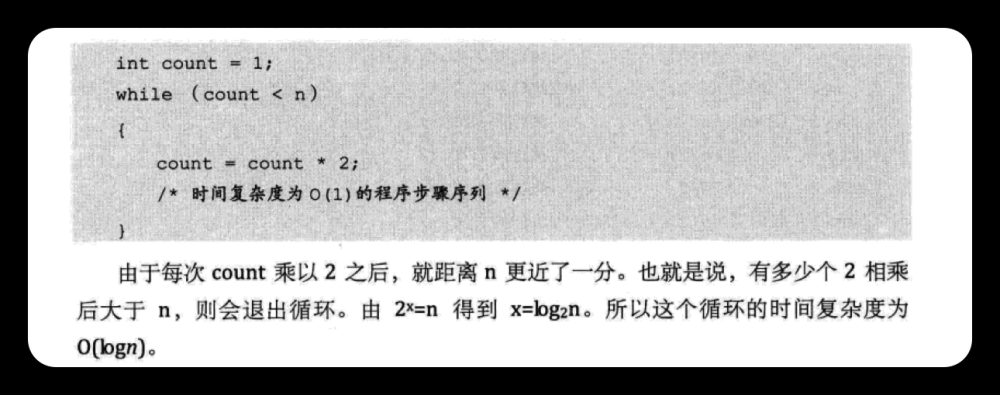

scan design的目的是使难以测试的时序电路变得类似较容易测试的组合电路。达到这个目的包括使用可扫描的时序元素(scan cells)替换时序元素,然后连接scan cells成为scan registers,或者是scan chains。然后在扫描模式下可以使用这些串连的scan cells来shift data in 和out。

图1中的设计包括组合和时序部分。在添加扫描之前,设计中有三个输入A、B、C和两个输出,OUT1和OUT2,是困难的去初始化已知状态,难以使用设计中的PI和PO控制内部电路并观察其行为。

添加了scan电路之后,设计多了两个额外的输入,sc_in和sc_en,一个额外的输出,sc_out,scan memory 元素取代初始的memory元素以至于当使能shift时,(sc_en有效),工具读入从sc_in读入扫描数据。

扫描电路的操作过程如下:

- 使能扫描操作来允许shifting(初始化scan cells)。

- 在加载scan cells之后,保持扫描时钟关闭,然后应用激励到Primary inputs。

- 测试outputs。

- 脉冲时钟来捕获新的值进入scan cells。

- 使能扫描操作来卸载和测试captured值,同时通过shift程序载入新的值。

About Scan Design Methodology

下图给出scan design的标志性代表。黑色长方形表示scan elements,线连接的为scan path。因为这是scan design,所有存储元素被转换和连接成scan path。空白盒子为电路的组合部分。

使用scan方法的优点:

- 高度自动化过程

当使用扫描插入工具时,插入扫描电路到设计的过程是高度自动化的,要求很少的手动操作。 - 高有效,可预测方法

scan design是高有效的,容易理解和接受的方法来得到设计的高覆盖率。 - 容易使用

使用扫描方法,可以不需要测试工程师的帮助来插入扫描电路和运行ATPG。 - 保证质量

scan保证了质量,因为芯片中包含扫描测试的部分可以被完全测试。

About Wrapper Chains

ATPG过程非常大,复杂设计经常是不可预测的。对于大型时序扫描或部分扫描设计,这个问题尤其真实,为了减少这种不可预测性,大量用于测试结构插入和测试生产的分成计术开始出现,创建wrapper chain就是其中一种技术,大的设计被分为许多design blocks,从wrapper chains中受益最多。

wrapper chains通过hier wrapper scan chain来增加设计的控制性和观察性,一个wrapper chain是设计部分的边界附近的一些列scan cells连接而成的,可在设计水平访问,wrapper chain通过转换输入输出点的时序元素为scan cells来提高coverage和减少运行时间。

下图设计中包含三个部分A、B和C。图中部分A的输入和输出在design level不能直接控制和观察,因为不能在design level直接访问,被这些pins控制的电路可能会造成设计的可测试性问题。

下图在部分A上添加了wrapper chian结构,增加了部分A的可控制性和可观测性。

只有直接连接到不可控制的PI和不可观测的PO的第一个elements会变成wrapper chain的一部分。

wrapper chain由两种类型的elements组成:直接连接到不可控制的PI的时序元素,和直接连接到不可观察的PO的时序元素。还要求两个design-level的pins,scan in和scan out,可以直接访问先前不可控制的或不可观察的电路。

也可以使用wrapper chains连接scan结构,不被包含在wrapper chains中的时序元素变成internal scan的candidates。

Wrapper Cellls Analysis

Tessent Scan通过减少设计子模块的内部core scan chains来提高层次化设计的性能和test coverage。在top-level只要求测试submodules的logic inputs必须是使用scan chains可控制的(必须被寄存器所驱动),logic outputs必须是通过scan chains可观察的(必须可registered)。

使用wrapper scan chains可满足这些要求,wrapper chains在submodiles外围的scan chains,连接每个input和output。工具将包括从submodules的inputs可到达的wrapper cells的wrapper chains处理为input型wrapper chians,将包括从submodules的outputs可达到的wrapper cells的wrapper chains处理为output型wrapper chians。使用input和output wrapper chians在INTEST和EXTEST模式期间提供高的层次测试覆盖率。

在INTEST mode,所有到submodules的inputs都是使用input wrapper chains可控制的,所有outputs是都是使用output wrapper chains可观察的,提供了为submodules独立生成完整ATPG的能力。

在EXTEST模式下,从submodules来的所有outputs都是使用output wrapper chians可控制的,所有inputs都是使用input wrapper chains可观察的。这提供了在top-level对围绕submodules的logic进行测试/优化的能力,而不需要对submodules进行内部可见性(即不需要core scan chains)。

analyze_wrapper_cells命令标识shared scan cells和dedicated wrapper cells(为了提高可测试性专门加的寄存器?)在top level测试期间提供完整的PI可观察性和PO可控制性。此外,在internal mode,input wrapper cells从PI完全隔离core,output wrapper cells为core的internal nodes提供了可观察性。

该工具将scan cells的scan使能端连接与intest使能信号结合起来(?),以防止这些scan cells在intest期间capture来自PI的任何值。将scan cells的scan_enable连接与extest mode capture数据,各mode的行为如下表所示:

下面段落wrapper analysis 算法的高级描述以解释为什么工具选择dedicated wrapper cells而不是shared wrapper cells为了PI和PO。

工具从PO pins开始反向追溯,如果在反向追溯过程中遇到的scan cells的数量超过了特定的阈值,那么它将插入一个dedicated wrapper cells。此外,在extest 测试时,output wrapper cells的set和reset引脚必须是可控的,这意味着该工具需要从潜在的shared wrapper cells的set和reset pins进行追溯,以查看是否由更多的scan cells可能影响这些pins,并将它们视为额外的output wrapper cells,如果组合连接的scan cells的数量,加上set和reset端口反馈路径中的scan cells超过了某个阈值,那么工具再次使用插入dedicated wrapper cells。

工具会对每一个PI执行相似的分析,如果通过特定PI达到的scan cells的数量超过指定的阈值,那么会使用一个dedicated wrapper cell。对于input wrapper cells,工具必须知道scan cell的所有ports的值,这意味着除了set和reset之外还必须从时钟和data port进行追溯,以查找必须成为wrapper cell的任何scan cells。如果组个连接scan cells的数量,以及在set、reset、clock等反馈路径上的scan cells的数量超过指定的阈值,那么工具插入一个dedicated wrapper cell。在反馈路径上的cells必须在测试期间保持完全可控制,并且它们大多数可能从non-wrapper scan wells中capture值,这意味着工具必须标记这些cells作为output wrapper cells,因为它们连接到内部的生成的scan使能信号,在capture期间保持为高电平。

所有的追溯是基于追溯通过unblocked paths发生的,这 意味着pin约束能够对这个分析有大的影响,例如,如果output wrapper cell的set和reset端口因为pin的约束而保持一个常数0,,那么不需要反向追溯。

可以使用set_dedicated_wrapper_cell_options命令在任何端口强制插入一个wrapper cell,此外,有几个参数控制向前和向后追溯,可以使用set_wrapper_analysis_options命令更改。

有几个条件可以触发工具插入dedicated wrapper cells或者留下unwrapped的端口,工具在下面几种情况下插入dedicated wrapper:

- 如果wrapper anasis超过使用set_wrapper_analysis_options定义的阈值。

- 如果追溯到达现存scan chain的scan cell。

- 如果追溯到blackbox,并且set_wrapper_analysis_options -register_ports_reaching_blackboxes被设置为all或者明确提供blackbox给switch(否则工具会忽略到达blackboxes的fanout分支)。

- 如果追溯到一个scan element,其internal_scan_only属性设置为true。

- 如果追溯到scan segment,并且set_wrapper_analysis_options -allow_internal_segments_as_wrapper被设置为off(否则,工具转换segment和scan elements为shared wrapper cells)。

- 如果输出端口是floating(输出悬空),并且set_wrapper_analysis_options -register_undriven_output设置为on。

工具可能在下面几种情况下留下unwrapped port:

- 如果input port没有驱动任何时序单元。

- 如果时钟端口,ICL端口(指的是ijta_se/ijtag_en一系列端口)、DFT信号(scan_en、edt_update)、bidi端口、或者测试相关端口(例如扫描使能端口)。

- 如果只到达ICL instruments,且keep_active_during_scan_test属性被设置为true(sib_sri,ssan resource Instruments)。

- 如果一个floating output,且set_wrapper_analysis_options -register_undriven_output被设置为off。

Wrapper Chains Generation

Tessent Scan单独生成input和output wrapper chains

input和output wrapper chains基于以下条件生成:

- 使用set_wrapper_analysis_options和analyze_wrapper_cells命令识别包括wrapper scan chains的scan cells为input 和output wrapper cells,使用insert_test_logic命令连接到单独的input和output wrapper chains上。

Test Structure Insertion With Tessent Scan

Tessent Scan Mentor Graphics internal 扫描综合工具,能够识别时序元素转换为scan cells,然后连接scan cells为scan chains。

Tessent Scan 包括以下features:

- Verilog fomat

读取或写出Verilog门级网表 - Multiple scan types

支持插入两种不同的scan types或方法:mux-DFF和clocked-scan(?) - Multiple test structrues

支持识别和扫描、wrapper chains和teset points插入。 - Scannability checking

为设计中的时序元素提供强大的扫描性检查/报告的能力(某元素是否是可扫描的)。 - Design rules checking

在实际插入scan之前,执行DRC检查以确保scan setup和operation是正确的,该DRC检查还能保证通过Tessent Scan所做的扫描插入在ATPG工具中功能正常(scan 插入的内容在做ATPG时能正常使用)。 - Interface to ATPG tools

自动为ATPG工具生成信息,这些信息是如何操作Tessent Scan 创建的scan circuitry。 - Optimal partial scan selection(?)

提供最佳的部分扫描分析和插入能力 - Flexible scan configurations

在扫描连接过程中使能灵活性,例如以固定或任意顺序连接scan cells,创建单个或多个scan chains,在单个扫描链上使用多个时钟。 - test logic

在不可控制的set、reset、clock,tri-state enable、RAM 读/写控制线上插入测试逻辑电路。 - User specified pins(?)

启用用户指定的测试和其他I/O引脚的名称。 - Multiple model levels

处理门级,以及门/晶体管级模型。 - Online help

ATPG Overview

ATPG表示自动测试向量生成,Test patterns,是在制造测试过程中放置在PIpins上的一组1或0以确定芯片是否有正确的功能。当应用测试向量的时候,ATE通过比较无故障输出(也被包含在test pattern中)与ATE实际测到的输出,来确定是否无制造缺陷。

The ATPG Process

ATPG的目的是创建一系列pattern来实现给定的test coverage,其中test coverage是pattern集实际检测到的可测试故障的总百分比。

ATPG主要包括两个步骤:1)生成patterns,2)执行故障仿真来确定以确定pattern可以检测到哪些故障。Mentor Graphics ATPG工具自动化将这两个步骤为单个操作或者ATPG process。产生的patterns可以通过添加的特定于测试仪的格式保存,是测试仪能够将patterns数据加载到芯片的扫描单元中,并正确应用patterns。

两个最经典的pattten生成的方法是random和deterministic,工具可使用来自外部集的pattern进行故障仿真,将这些patterns放入测试集中检测故障。

Random Pattern Test Generation

当ATPG工具产生大量的随机patterns,并且只识别检测故障的这些patterns时使用random pattern test generation,然后存储这些patterns到test pattern set中(能检测到故障的pattern)。

在random pattern test generation使用的故障仿真类型不能替代deterministic test generation,因为,它不能识别冗余故障,也不能为检测性低(非常低的可能性被检测到)的故障创建测试patterns,但是对于被deterministic test generation终止的(?)的可测试故障是有用的。作为初始步骤,使用少量random patterns可能提高ATPG的性能。

Deterministic Pattern Test Generation

当工具创建一个测试向量,目的是检测一个给定故障的时候使用deterministic test pattern generation。程序从故障列表中选择故障,创建一个pattern来检测fault,故障仿真pattern,并检查确保pattern检测到故障。

更加特别地是,工具分配一组值到控制点,强迫fault site具有于无故障状态相反的状态,因此可以检测到故障值和无故障值之间的差异。然后工具必须找到能够传播这个差异到一个点的方式,这个点可以观察故障效应。为了满足创建测试pattern的必要条件,test generation process决定如何最好地在gate上放置想要的值,如果冲突阻止在gate上放置这些值,工具将在尝试找到成功的测试pattern时改进这些decisions。

如果工具没有找到成功的test pattern,必须要在故障划分之前进一步分析,需要此分析的故障包括冗余、ATPG-untestable和possible-detected-untestable类别。识别这些故障时deterministic test generation的重要副产品,对于实现高测试覆盖率至关重要。例如,如果工具证明了一个故障时多余的,那么它就可以安全地将该故障标记为不可测试,否则,它被归类为一个潜在地可检测故障,并在计算测试覆盖率时计算为一个为测试的故障。

External Pattern Test Generation

当ATPG的preliminary source是现存的一组external patterns时,ATPG工具使用external pattern test generation。

工具分析external pattern set来确定哪些patterns从有效故障列表中检测故障,然后将有效的patterns放到internal test patterns中,在这种情况下,“generated patterns”包括从external set中选择的patterns,可以为设计有效地得到最高的测试覆盖率。

Mentor Graphics ATPG Applications

Tessent FastScan和Tessent TestKompress是Mentor Graphics 扫描时序的ATPG产品,与在Tessent Shell中操作“patterns -scan” context相同。

Scan Sequential ATPg With the ATPG Tool

Mentor Graphics ATPG产品包括许多特性,支持scan sequential ATPG(?scan sequential ATPG)

扫描工具中包括的scan sequential ATPG特性:

- 为具有结构化扫描的设计提供高性能ATPG。

- 使用distributed ATPG(?)减少run time而不会影响coverage和pattern数量。

- 通过最小化被false和multicycle paths造成的X的影响以最大化测试coverage。

- 使用全面的设计规则检查尽早识别可测试性问题。

- 通过自动仿真mismatch debugging以减少测试验证时间。

- 通过集成进所有的设计流程和foundary支持,确保更短的上市时间。

- 具有广泛的故障模型支持,包括stuck-at,IDDQ、transition,path delay和bridge。

- 对于准确的at-speed测试具有on-chip PLL支持。

- 通过scan自动测试小型嵌入式memories和cores。

- 被Tessent SoCScan 层次硅支持(就是支持层次化设计吧)。

Overview of Test Types and Fault Models

制造缺陷是发生在制造过程期间的物理问题,导致设备的功能异常,test generation的目的是创建一系列test patterns,尽可能多的检测制造缺陷。

下图给出了可能的缺陷类型,每一种缺陷对应相关的检测方法。

Test Types

有三种测试类型:functional、IDDQ和at-speed。functional testing检测输出pins的logic level的“0”和“1”响应。IDDQ测试通过电路设备的电流。At-speed testing检测设备改变逻辑状态的时间量。

Functional Test

Functional test仍然是最广泛接受的测试类型,Functional test通常由user-generated patterns, simulation patterns和ATPG patterns。

Functional testing在device input pins上使用logic level(1或者0),以煎炒在制造过程中最常见的问题,静态缺陷(例如,开路、短路、stuck-on、和stuck-open)。测试output pins上的逻辑结果(1或者0),通常,缺陷会导致output pins上的逻辑值与预期值不同。

IDDQ Test

IDDQ testing测量静态电源电流而不是pin电压,检测不容易被functional testing检测到的device failures,例如CMOS晶体管的stuck-on faults或者邻近bridging faults。IDDQ testing设备应用一组patterns,使电流稳定,然后测量过大电流,devices存在过大电流可能有内部制造缺陷。

因为IDDQ测试不会想output pins传播值,为了检测和测量高百分比故障的测试向量集使高度压缩的。ATPG工具有效地创建该压缩测试向量集。

此外,IDDQ测试可以检测一些静态故障,测试可靠性,并减少所需地老化测试次数,可以通过IDDQ测试增加测试来增加整体测试覆盖率。

IDDQ test generation方法分为几类:

-

Every-vector

这种方法为functional或者stuck-at 故障测试集中的每个向量提供电源电流监测。不幸的是,这种方法较慢,在制造环境中不实际。 -

Supplemental

该方法通过使用较小的IDDQ测量test vectors来增加现有的test set,从来bypass时间限制。

At-Speed Test

当电路在slow clock速率下正常工作,在系统时钟速率下运行可能发生时序失败,由于制造过程中的统计变量,导致部分导电晶体管和电阻桥缺陷,使芯片中存在延迟变化。

at-speed测试的目的使为了检测这些类型的问题,At-speed在正常系统时钟下执行测试。

Fault Modeling Overview

Faults models是在设计的逻辑模型中抽象表示制造缺陷的一种手段,每一种测试类型,对应不同组的defects。

Test Types and Associated Fault Models

Fault Locations

默认情况下,faults在library models的inputs和outputs点,但是如果set_internal_fault on,faults驻留在library models内的gates的inputs和outputs处。

要定位故障点,需要唯一的,hier instance的路径加上pin的名字。

也可以使用Verilog的celldefine来扩展library models的单元边界,使用这种技术有几种含义:

- 默认fault population改变。默认情况下,所有faults位于library边界引脚处,但是当library边界从ATPGlibrary level达到celldefine level是,faults的位置和population会改变。

- flattened model可以是不同的,因为celldefile module内部的逻辑可能被优化以减少flattened 的模型尺寸。

- celldefine内部的hier instance/pin names不会被看作合法的instance/pin names。

Fault Collapsing

电路中包含大量的故障和其他的故障行为相同,测试可能识别一个故障,但是可能不能将它与其他故障区分,在这种情况下,故障被认为是等价的,故障识别过程将故障减少为一个等效故障,这一过程称为fault collapsing。文章来源:https://www.toymoban.com/news/detail-679871.html

出于性能的原因,在故障识别过程的早期,ATPG工具会从等价故障集中挑出一个,并在后续算法中使用这个代表性的故障。同样出于性能原因,这个应用在故障仿真和测试pattern生成期间只评估一个等效故障或折叠故障,然而,这些工具保留了关于collapsed和uncollapsed的故障,因此它们仍然可以生成故障报告和测试覆盖率计算。文章来源地址https://www.toymoban.com/news/detail-679871.html

到了这里,关于第二章:Scan and ATPG Basics的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!