时钟

首先我们需要知道我们生成时钟的需求如下。

然后知道设计要点

dft可控:表示在dft模式下,我们选择外部的测试时钟而不是芯片内部的pll的时钟。这个外部的时钟可以被dft工程师控制。

dft隔离:表示在scan的情况下,很多寄存器会上链,所以输出不定,但是这些输出又去驱动了很多重要的系统模块,这个时候我们需要使用mux将寄存器的输出固定。

dft观测:这些内部产生的时钟需要送到pad做到可观测,看是否符合要求。

外部参考时钟:PLL是倍频电路,它会使用晶振产生的参考时钟比如10m进行倍频。倍频需要稳定时间, pll输出lock信号表示倍频后的时钟稳定了,可以被芯片使用,但是在lock信号之前,pll的输出时钟不稳定,这个时候需要外部的时钟作为芯片的主时钟。所以涉及到一个无毛刺的切换电路。

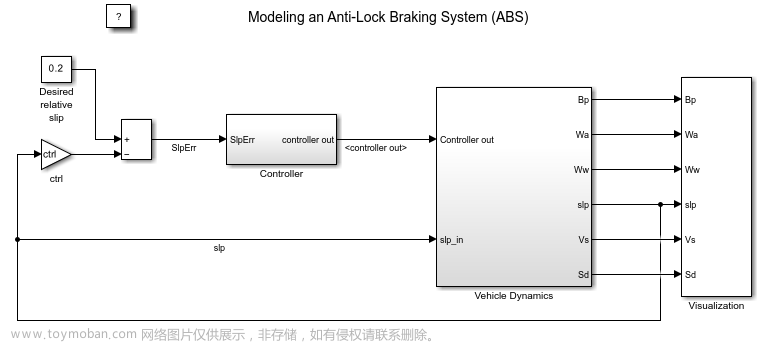

时钟图

1. 首先从模拟进入osc_in=8M,这是ref-clk。然后8m的时钟进入到pll倍频。倍频结束之前我们使用的是8m的参考时钟,倍频结束之后我们才能使用倍频时钟。所以这里有一个无毛刺切换。

2. 无毛刺切换后就是sys_clk,对它进行分频。注意这里的apb也需要分屏,图中已经标出来了。

无毛刺切换电路

3. 图中dft_mode下的32‘{1’b0},1’b0,4{1‘b0}会在dft模式下插入自己的配置数,前端看不到,这就是dft可控。

4. ICG模块和occ模块。

ICG就是门控单元,E端为clk负沿采样en。采样之后的信号和clk进行与,这样做的好处是无论en在clk的什么地方拉高都不会切出毛刺,得到的gclk都是完整的时钟。

5.分频电路 8192分频电路,2^13=8192,所以使用12bit位。这里:先将sys_clk分频,再将分频后的脉冲作为sys_clk的门控,产生分频后的时钟。这是标准做法。设定一个bit数13的寄存器。

使用rtc_clk_div作为icg的门控。生成的rtc_clk_pre就是clk_pll_in的8192分频时钟。

同理,2,4,8,16分频。2^4=16,所以bit3就可以表示16分频。

使用ahb_clk_div作为icg的门控。

OCC模块(片上时钟控制器)

occ一般插在功能时钟pll的后面,它的位置如下图。

occ的功能如下:

1. 切换功能时钟和测试时钟

2.为ac scan 提供正确数量的功能时钟脉冲。

3. 每个时钟域独立控制。

occ内部结构

测试模式信号:0功能模式1测试模式

ac模式信号:0dcscan 1acscan

扫描信号:慢速scan扫描信号

参考时钟 8m,经过pll后为sys_clk

扫描时钟:慢速scan时钟

occ工作状态图

1.测试模式信号为0,occ输出功能clk。

2. 测试模式信号为1,ac 模式信号无论1还是0,扫描信号为1,occ输出慢速scan_clk。

首先将扫描信号置位1表示慢速scan模式,在此模式下填充寄存器,如果想要两个功能时钟(全速时钟)的脉冲,就通过mux扫描输入pattern将四个寄存器变成1100,如果想要3个,就变成1110。然后在切换扫描信号为0,这个时候两个快速时钟会送出,最后又将扫描信号置位1,输出慢速时钟。

总结:scan_en-->>1,0,1。

scan的移入捕获移出操作

为什么上面的时钟只有两个上升沿?这需要从dft的scan操作说起。

在移入操作时,使用慢速的时钟,将10011送入上排的5个寄存器,同时01001从组合逻辑送出,因为组合逻辑的计算是没有延迟的。 进入捕获操作,这个时候如果是要检测stuck at这类的静态测试,可以使用慢速时钟(和之前的移入时钟一样的频率也是可以的)。如果检查跳变和延迟故障,需要使用功能时钟,尽量准确的模拟功能的情况下luanch和capture的情况去检测timing path。下图就是stuck at问题中使用的捕获时钟和移入移出一样频率。

下图是检查跳变和延迟故障时候的捕获时钟为功能时钟也叫做全速时钟。但是需要注意,这个se是一个全局信号,它会送到所有芯片寄存器的se端口,这样从si进来的数据很可能不能满足建立和保持时间,因为这个时候的全速时钟非常快,这对时序有很大挑战。

但是,如果像下图这样在第一个全速时钟之前拉低se,之前应该从si来的数据便从下面第二个图中的第二排寄存器的d端来了。下面第二个图中,se的拉低后的launch沿把数据从第一个组合云送到第二排寄存器,在经过capture沿打入第三排寄存器。虽然多了一组组合逻辑但是依然可以使用算法检测出dft问题,大大减少了时序压力。

复位

下面是复位的需求,注意每个外设应该有一个软复位,在外设出问题的时候,可以单独复位。

dft可控就是有些和复位相关的寄存器上链后,来回toggle,会导致scan模式下不停复位,所以我们需要做dft隔离。dft可控就是dft工程师可以插入dft复位使得芯片复位。

设计要求

复位电路如下:

HARD_RST_N从pad过来。经过滤波之后和内部其他复位与之后生成全局复位,全局复位在各自时钟域下同步,pbus_rst_n还要在与上软复位。软复位由寄存器来,也需要dft的隔离。

dft复位可控的代码

mux U_SYS_RESET_DFT_CTRL(

.A(hard_rst_n_in) //实际复位

.B(dft_crg_rst_n) //DFT使用的复位,悬空在core层

.S0(dft_mode)

.Y(dft_hard_rst_n_in)

);

滤毛刺代码 flt_out_rst为滤毛刺之后的代码。

always @(posedge sys_clk or negedge dft_hard_rst_n_in) begin

if (~dft_hard_rst_n_in) begin

dft_hard_rst_n_in_sync<={8{1'b0}};

end

else begin

dft_hard_rst_n_in_sync <={dft_hard_rst_n_in_sync[6:0],1'b1};

end

end文章来源:https://www.toymoban.com/news/detail-679917.html

assign flt_out_rst=| dft_hard_rst_n_in_sync;文章来源地址https://www.toymoban.com/news/detail-679917.html

到了这里,关于MCU集成-时钟复位控制的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!