一 象征性啰嗦

想必大家在刚开始尝试写Verilig HDL代码的时候,都是参考一些列参考代码,有些来自于参考书,有些来自于网上大牛的笔记,甚至有写来自于某宝FPGA开发板的授权代码。我还记得自己当时第一次写代码,参考的是一款Altera 芯片,结合Quartus 开发软件, 在上面练习代码,然后综合等等。

其实,当初也是一味照本宣科的临摹,而对于为什么那么些,代码又是内部有什么含义,并没有深入理解。这里面的东西太多,想到哪里,就记到哪里吧。大家见谅!

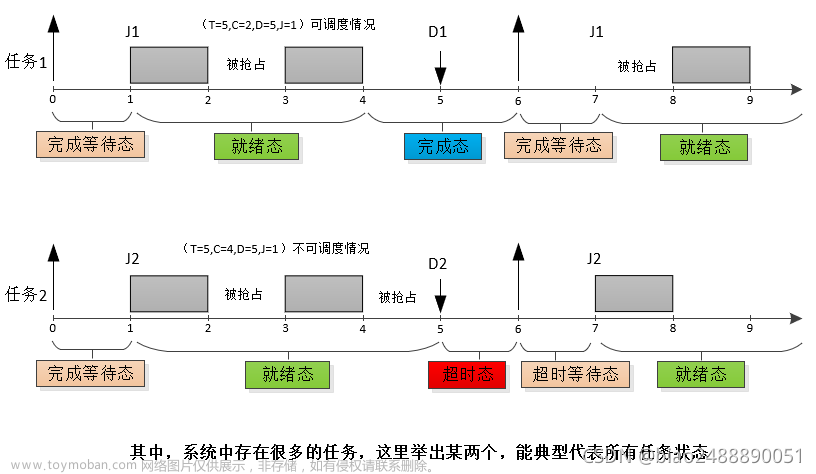

对于寄存器,大家用的是最多的。从最初的存储数据,到后期的异步时钟域处理打拍设计。而对于寄存器的采样问题,也仅仅是流于表面。何时采样?采样数据是哪里?都没有搞清楚。今天,我们一起来学习一下,到底怎么回事。

二 代码逐行分析

2.1 同步时钟采样

如上代码,第28~31行,cnt 计数寄存器在每个时钟上升沿到来时,进行加一并赋值。

第33~36行代码,在同一时钟边沿时刻,对cnt 计数寄存器进行采样,并将采样结果保存在cnt_delay 寄存器中。文章来源:https://www.toymoban.com/news/detail-682445.html

针对这种情形,书籍只是告诉我们:这样设计代码,能够完成计数器的打拍。当时就有疑问:两段代码不是采用同一个时钟clk 吗,clk 边沿到来时,cnt 在变化,为什么采样的是cnt 旧数据呢?文章来源地址https://www.toymoban.com/news/detail-682445.html

<到了这里,关于#systemverilog# 之 event region 和 timeslot 仿真调度(六)疑惑寄存器采样吗的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!