RISCV - 1 RV32/64G指令集清单

RISCV - 2 “Zicsr“, CSR Instructions

RISCV -3 RV32I/RV64I基本整型指令集

RISCV - 4 ISA 扩展名命名约定

RISCV 5 RISC-V调用规则

1 RV32I Load and Store Instructions

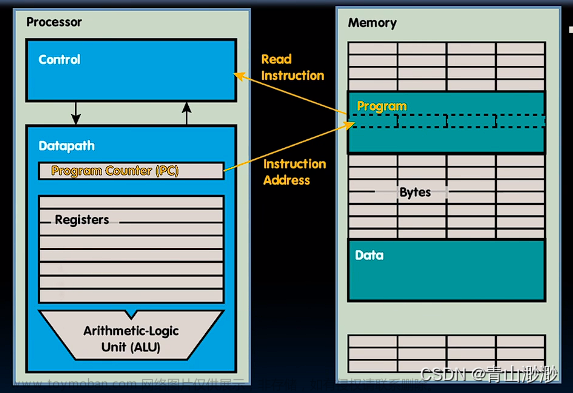

RV32I is a load-store architecture, where only load and store instructions access memory and arithmetic instructions only operate on CPU registers. RV32I provides a 32-bit address space that is byte-addressed. The EEI will define what portions of the address space are legal to access with which instructions (e.g., some addresses might be read only, or support word access only). Loads with a destination of x0 must still raise any exceptions and cause any other side effects even though the load value is discarded.

RV32I 是一种加载-存储架构,只有加载和存储指令才能访问内存,算术指令只能在 CPU 寄存器上运行。RV32I 提供字节寻址的 32 位地址空间。EEI 将定义地址空间的哪些部分可以用哪些指令合法访问(例如,某些地址可能只允许读取,或只支持字访问)。目标地址为 x0 的加载,即使加载值被丢弃,仍必须引发任何异常并导致任何其他副作用。

The EEI will define whether the memory system is little-endian or big-endian. In RISC-V, endianness is byte-address invariant.

EEI 将定义内存系统是小端位(little-endian)还是大端位(big-endian)。在 RISC-V 中,字节地址不变。

In a system for which endianness is byte-address invariant, the following property holds: if a byte is stored to memory at some address in some endianness, then a byte-sized load from that address in any endianness returns the stored value.

在一个字节地址不变的系统中,存在以下特性:如果一个字节被存储到内存的某个字节地址上,那么在任何字节地址上从该地址进行字节大小的加载都会返回存储的值。

In a little-endian configuration, multibyte stores write the least-significant register byte at the lowest memory byte address, followed by the other register bytes in ascending order of their significance. Loads similarly transfer the contents of the lesser memory byte addresses to the less-significant register bytes.

在 little-endian 配置中,多字节存储将最低有效位的寄存器字节写入最低的内存字节地址,然后按最高有效位递增顺序写入其他寄存器字节。载入时,同样将较小内存字节地址的内容转移到最低有效位的寄存器字节。

In a big-endian configuration, multibyte stores write the most-significant register byte at the lowest memory byte address, followed by the other register bytes in descending order of their significance. Loads similarly transfer the contents of the greater memory byte addresses to the less-significant register bytes.

在 big-endian 配置中,多字节存储将最高有效位的寄存器字节写入最低的内存字节地址,然后按有效位程度降序写入其他寄存器字节。载入时,同样将较大内存字节地址的内容转入较小寄存器字节。

The LW instruction loads a 32-bit value from memory into rd. LH loads a 16-bit value from memory, then sign-extends to 32-bits before storing in rd. LHU loads a 16-bit value from memory but then zero extends to 32-bits before storing in rd. LB and LBU are defined analogously for 8-bit values.

LW 指令将内存中的 32 位数值加载到 rd 中。LH 从内存中载入 16 位数值,然后符号扩展到 32 位,再存入 rd。LHU 从内存加载一个 16 位数值,但在存储到 rd 之前将零扩展到 32 位。LB 和 LBU 的定义与 8 位值类似。

The SW, SH, and SB instructions store 32-bit, 16-bit, and 8-bit values from the low bits of register rs2 to memory.

SW、SH 和 SB 指令将寄存器 rs2 低位的 32 位、16 位和 8 位数值存储到内存中。

1.1 LOAD instructions

Loads are encoded in the I-type format

加载指令以 I 型格式编码

I类型指令编码格式:

1.1.1 加载指令的指令格式

加载指令的编码格式

其对应的立即数的编码格式如下所示:

- 立即数的bit0从在加载指令的bit[20]位去获取,bit1-4是从加载指令的bit[24:21]获取,而bit 5~10则是从加载指令的bit[30:25]获取,符号位则是加载指令的bit[31],立即数的 bit11 ~31都按照加载指令的bit[31]做符号扩展。

1.1.2 加载指令在使用时需要注意的点

加载指令时I类型的指令编码,其立即数是有符号的立即数,在处理时需要考虑其符号位,立即数的范围为[-2048 ~ 2047]

因此当使用加载指令去处理offset小于-2048以及大于2047时会报offset的异常错误。lb t1, (-2048 ~ 2047)(t0)是合法的加载指令

而lb t1, -2049(t0)或者lb t1, 2048(t0)则是非法加载操作。

1.2 STORE instructions

Stores are encoded in the S-type.

存储指令以 S 类型编码。

1.2.1 存储指令的指令格式

存储指令的指令格式

其对应的立即数的编码格式如下所示:

- 立即数的bit0从在加载指令的bit[7]位去获取,bit1-4是从加载指令的bit[11:8]获取,而bit 5~10则是从加载指令的bit[30:25]获取,符号位则是加载指令的bit[31],立即数的 bit11 ~31都按照加载指令的bit[31]做符号扩展。

1.2.2 存储指令在使用时需要注意的点

存储指令时S类型的指令编码,其立即数是有符号的立即数,在处理时需要考虑其符号位,立即数的范围为[-2048 ~ 2047]

因此当使用加载指令去处理offset小于-2048以及大于2047时会报offset的异常错误。sw t1, (-2048 ~ 2047)(t0)是合法的加载指令

而sw t1, -2049(t0)或者lb t1, 2048(t0)则是非法加载操作。

2 RV64 Load and Store Instructions

RV64 的加载存储指令和RV32的加载存储指令时类似的。

RV64I extends the address space to 64 bits. The execution environment will define what portions of the address space are legal to access.

RV64I 将地址空间扩展到 64 位。执行环境将确定地址空间的哪些部分可以合法访问。

Load byte(lb):从内存中加载一个字节并将其扩展为32位。例如,lb x1, 0(x2)表示从寄存器x2指向的地址偏移0处的内存位置加载一个字节,并将其扩展为64位后存储在寄存器x1中。

Load half-word(lh):从内存中加载半个字(16位)并将其扩展为32位。例如,lh x1, 0(x2)表示从寄存器x2指向的地址偏移0处的内存位置加载一个半个字,并将其扩展为64位后存储在寄存器x1中。

Load word(lw):从内存中加载一个字(32位)。例如,lw x1, 0(x2)表示从寄存器x2指向的地址偏移0处的内存位置加载一个字,并将其扩展为64位后存储在寄存器x1中。

Load double-word(ld):从内存中加载两个字(64位)。例如,ld x1, 0(x2)表示从寄存器x2指向的地址偏移0处的内存位置加载一个双字,并将其存储在寄存器x1中。

Store byte(sb):将一个字节存储到内存中。例如,sb x1, 0(x2)表示将寄存器x1中的低8位存储到从寄存器x2指向的地址偏移0处的内存位置。

Store half-word(sh):将半个字存储到内存中。例如,sh x1, 0(x2)表示将寄存器x1中的低16位存储到从寄存器x2指向的地址偏移0处的内存位置。

Store word(sw):将一个字存储到内存中。例如,sw x1, 0(x2)表示将寄存器x1中的值存储到从寄存器x2指向的地址偏移0处的内存位置。

Store double-word(sd):将两个字存储到内存中。例如,sd x1, 0(x2)表示将寄存器x1中的值存储到从寄存器x2指向的地址偏移0处的内存位置

2.1 Load Instructions

The LD instruction loads a 64-bit value from memory into register rd for RV64I.

LD 指令将内存中的 64 位值加载到 RV64I 的寄存器 rd 中。

2.2 Store Instructions

文章来源:https://www.toymoban.com/news/detail-682539.html

文章来源:https://www.toymoban.com/news/detail-682539.html

The SD, SW, SH, and SB instructions store 64-bit, 32-bit, 16-bit, and 8-bit values from the low bits of register rs2 to memory respectively.

SD、SW、SH 和 SB 指令分别将寄存器 rs2 低位的 64 位、32 位、16 位和 8 位数值存储到内存中。文章来源地址https://www.toymoban.com/news/detail-682539.html

到了这里,关于RISCV 6 RISC-V加载存储指令的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!