1、前言

没玩过GT资源都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。

GT资源是Xilinx系列FPGA的重要卖点,也是做高速接口的基础,不管是PCIE、SATA、MAC等,都需要用到GT资源来做数据高速串化和解串处理,Xilinx不同的FPGA系列拥有不同的GT资源类型,低端的A7由GTP,K7有GTX,V7有GTH,更高端的U+系列还有GTY等,他们的速度越来越高,应用场景也越来越高端。。。

本文使用Xilinx的Kintex7 FPGA的GTX资源做视频传输实验,视频源有两种,分别对应开发者手里有没有摄像头的情况,一种是使用笔记本电脑模拟HDMI视频,IT6802解码输入的HDMI为GRB后供FPGA使用;如果你得手里没有摄像头,或者你得开发板没有HDMI输入接口,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的`define宏定义进行,默认使用HDMI输入作为视频源;调用GTX IP核,用verilog编写视频数据的编解码模块和数据对齐模块,使用开发板硬件上的2个SFP光口实现数据的收发;本博客提供2套vivado工程源码,2套工程的不同点在于使用1个SFP光口做收发还是两个2个SFP光口做收发;本博客详细描述了FPGA GTX 视频传输的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

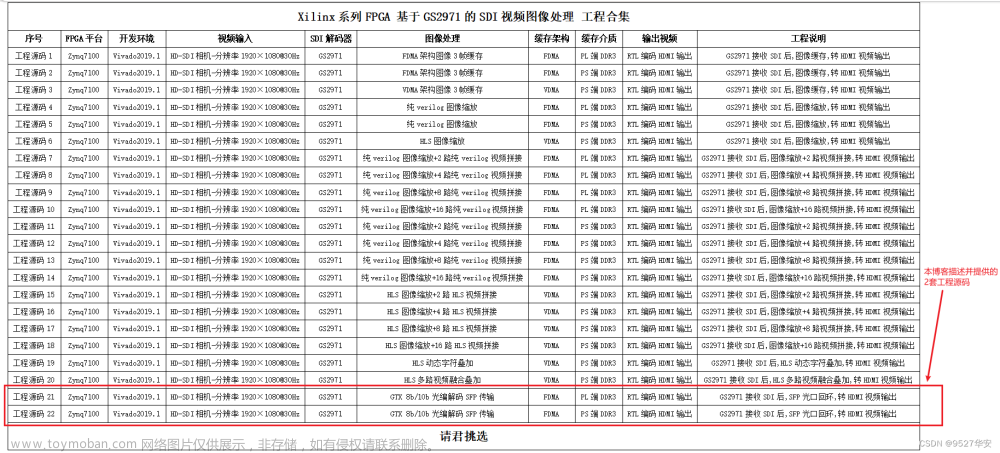

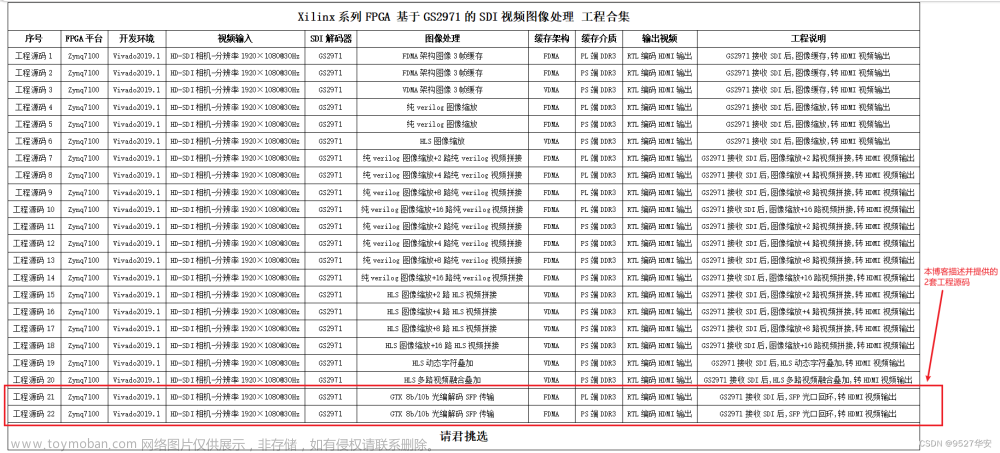

2、我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

3、GTX 全网最细解读

关于GTX介绍最详细的肯定是Xilinx官方的《ug476_7Series_Transceivers》,我们以此来解读:

《ug476_7Series_Transceivers》的PDF文档我已放在了资料包里,文章末尾有获取方式;

我用到的开发板FPGA型号为Xilinx Kintex7 xc7k325tffg676-2;带有8路GTX资源,其中2路连接到了2个SFP光口,每通道的收发速度为 500 Mb/s 到 10.3125 Gb/s 之间。GTX收发器支持不同的串行传输接口或协议,比如 PCIE 1.1/2.0 接口、万兆网 XUAI 接口、OC-48、串行 RapidIO 接口、 SATA(Serial ATA) 接口、数字分量串行接口(SDI)等等;

GTX 基本结构

Xilinx 以 Quad 来对串行高速收发器进行分组,四个串行高速收发器和一个 COMMOM(QPLL)组成一个 Quad,每一个串行高速收发器称为一个 Channel(通道),下图为四路 GTX 收发器在Kintex7 FPGA 芯片中的示意图:《ug476_7Series_Transceivers》第24页;

GTX 的具体内部逻辑框图如下所示,它由四个收发器通道 GTXE2_CHANNEL原语 和一个GTXE2_COMMON 原语组成。每路GTXE2_CHANNEL包含发送电路 TX 和接收电路 RX,GTXE2_CHANNEL的时钟可以来自于CPLL或者QPLL,可在IP配置界面里配置;《ug476_7Series_Transceivers》第25页;

每个 GTXE2_CHANNEL 的逻辑电路如下图所示:《ug476_7Series_Transceivers》第26页;

GTXE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

这里说多了意义不大,因为没有做过几个大的项目是不会理解这里面的东西的,对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用,后面我也会重点将到IP核的调用和使用;

GTX 发送和接收处理流程

首先用户逻辑数据经过 8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO),该缓冲区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速 Serdes 进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。这里的每一个功能点都可以写一篇论文甚至是一本书,所以这里只需要知道个概念即可,在具体的项目中回具体用到,还是那句话:对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用。

GTX 的参考时钟

GTX 模块有两个差分参考时钟输入管脚(MGTREFCLK0P/N 和 MGTREFCLK1P/N),作为 GTX 模块的参考时钟源,用户可以自行选择。一般的A7系列开发板上,都有一路 148.5Mhz 的 GTX 参考时钟连接到 MGTREFCLK0上,作为 GTX 的参考时钟。差分参考时钟通过IBUFDS 模块转换成单端时钟信号进入到 GTXE2_COMMOM 的QPLL或CPLL中,产生 TX 和 RX 电路中所需的时钟频率。TX 和 RX 收发器速度相同的话,TX 电路和 RX 电路可以使用同一个 PLL 产生的时钟,如果 TX 和 RX收发器速度不相同的话,需要使用不同的 PLL 时钟产生的时钟。参考时钟这里Xilinx给出的GT参考例程已经做得很好了,我们调用时其实不用修改;GTX 的参考时钟结构图如下:《ug476_7Series_Transceivers》第31页;

GTX 发送接口

《ug476_7Series_Transceivers》的第107到165页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲GTX例化时留给用户的发送部分需要用到的接口;

用户只需要关心发送接口的时钟和数据即可,GTX例化模块的这部分接口如下:

在代码中我已为你们重新绑定并做到了模块的顶层,代码部分如下:

GTX 接收接口

《ug476_7Series_Transceivers》的第167到295页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲GTX例化时留给用户的发送部分需要用到的接口;

用户只需要关心接收接口的时钟和数据即可,GTX例化模块的这部分接口如下:

在代码中我已为你们重新绑定并做到了模块的顶层,代码部分如下:

GTX IP核调用和使用

这里对上图的标号做解释:

1:线速率,根据自己的项目需求来,GTX 的范围是0.5到10.3125G,由于我的项目是视频传输,所以在GTX 的速率范围内均可,本例程选择了5.94G;

2:参考时钟,这个得根据你的原理图来,可以是80M、125M、148.5M、156.25M等等,我的开发板是148.5M;

4:GTX 组的绑定,这个很重要,他的绑定参考依据有两个,已是你的开发板原理图,而是官方的参考资料《ug476_7Series_Transceivers》,官方根据BANK不同将GTX资源分成了多组,由于GT资源是Xilinx系列FPGA的专用资源,占用专用的Bnak,所以引脚也是专用的,那么这些GTX组和引脚是怎么对应的呢?《ug476_7Series_Transceivers》的说明如下:红框内为的我的开发板原理图对应的FPGA引脚;

我的板子原理图如下:

选择外部数据位宽32bit的8b/10b编解码,如下:

下面这里讲的是K码检测:

这里选择K28.5,也就是所谓的COM码,十六进制为bc,他的作用很多,可以表示空闲乱序符号,也可以表示数据错位标志,这里用来标志数据错位,8b/10b协议对K码的定义如下:

下面讲的是时钟矫正,也就是对应GTP内部接收部分的弹性buffer;

这里有一个时钟频偏的概念,特别是收发双方时钟不同源时,这里设置的频偏为100ppm,规定每隔5000个数据包发送方发送一个4字节的序列,接收方的弹性buffer会根据这4字节的序列,以及数据在buffer中的位置来决定删除或者插入一个4字节的序列中的一个字节,目的是确保数据从发送端到接收端的稳定性,消除时钟频偏的影响;

4、设计思路框架

本博客提供2套vivado工程源码,2套工程的不同点在于使用1个SFP光口做收发还是两个2个SFP光口做收发;使用1个SFP光口做收发是用光纤连接SFP的RX和TX;使用2个SFP光口做收发是用光纤连接一个SFP的RX和另一个SFP的TX;设计思路框架分别如下:

使用2个SFP光口框图如下:

使用1个SFP光口框图如下:

视频源选择

视频源有两种,分别对应开发者手里有没有摄像头的情况,如果你的手里有摄像头,或者你的开发板有HDMI输入接口,则使用HDMI输入作为视频输入源,我这里用到的是笔记本模拟HDMI视频,IT6802解码芯片解码HDMI;如果你得手里没有摄像头,或者你得开发板没有HDMI输入接口,则可使用代码内部生成的动态彩条模拟摄像头视频,动态彩条是移动的画面,完全可以模拟视频;默认使用HDMI输入作为视频源;视频源的选择通过代码顶层的`define宏定义进行;如下:

选择逻辑代码部分如下:

选择逻辑如下:

当(注释) define USE_SENSOR时,输入源视频是动态彩条;

当(不注释) define USE_SENSOR时,输入源视频是HDMI输入;

IT6802解码芯片配置及采集

IT6802解码芯片需要i2c配置才能使用,关于IT6802解码芯片的配置和使用,请参考我往期的博客,博客地址:点击直接前往

IT6802解码芯片配置及采集这两部分均用verilog代码模块实现,代码位置如下:

代码中配置为1920x1080分辨率;

动态彩条

动态彩条可配置为不同分辨率的视频,视频的边框宽度,动态移动方块的大小,移动速度等都可以参数化配置,我这里配置为辨率1920x1080,动态彩条模块代码位置和顶层接口和例化如下:

视频数据组包

由于视频需要在GTX中通过aurora 8b/10b协议收发,所以数据必须进行组包,以适应aurora 8b/10b协议标准;视频数据组包模块代码位置如下:

首先,我们将16bit的视频存入FIFO中,存满一行时就从FIFO读出送入GTX发送;在此之前,需要对一帧视频进行编号,也叫作指令,GTX组包时根据固定的指令进行数据发送,GTX解包时根据固定的指令恢复视频的场同步信号和视频有效信号;当一帧视频的场同步信号上升沿到来时,发送一帧视频开始指令 0,当一帧视频的场同步信号下降沿到来时,发送一帧视频开始指令 1,视频消隐期间发送无效数据 0 和无效数据 1,当视频有效信号到来时将每一行视频进行编号,先发送一行视频开始指令,在发送当前的视频行号,当一行视频发送完成后再发送一行视频结束指令,一帧视频发送完成后,先发送一帧视频结束指令 0,再发送一帧视频结束指令 1;至此,一帧视频则发送完成,这个模块不太好理解,所以我在代码里进行了详细的中文注释,需要注意的是,为了防止中文注释的乱序显示,请用notepad++编辑器打开代码;指令定义如下:

指令可以任意更改,但最低字节必须为bc;

GTX aurora 8b/10b

这个就是调用GTX做aurora 8b/10b协议的数据编解码,前面已经对GTX做了详细概述,这里不讲;代码位置如下:

数据对齐

由于GT资源的aurora 8b/10b数据收发天然有着数据错位的情况,所以需要对接受到的解码数据进行数据对齐处理,数据对齐模块代码位置如下:

我定义的 K 码控制字符格式为:XX_XX_XX_BC,所以用一个rx_ctrl 指示数据是否为 K 码 的 COM 符号;

rx_ctrl = 4’b0000 表示 4 字节的数据没有 COM 码;

rx_ctrl = 4’b0001 表示 4 字节的数据中[ 7: 0] 为 COM 码;

rx_ctrl = 4’b0010 表示 4 字节的数据中[15: 8] 为 COM 码;

rx_ctrl = 4’b0100 表示 4 字节的数据中[23:16] 为 COM 码;

rx_ctrl = 4’b1000 表示 4 字节的数据中[31:24] 为 COM 码;

基于此,当接收到有K码时就对数据进行对齐处理,也就是将数据打一拍,和新进来的数据进行错位组合,这是FPGA的基础操作,这里不再赘述;

视频数据解包

数据解包是数据组包的逆过程,代码位置如下:

GTX解包时根据固定的指令恢复视频的场同步信号和视频有效信号;这些信号是作为后面图像缓存的重要信号;

至此,数据进出GTX部分就已经讲完了,整个过程的框图我在代码中描述了,如下:

图像缓存

经常看我博客的老粉应该都知道,我做图像缓存的套路是FDMA,他的作用是将图像送入DDR中做3帧缓存再读出显示,目的是匹配输入输出的时钟差和提高输出视频质量,关于FDMA,请参考我之前的博客,博客地址:点击直接前往

视频输出

视频从FDMA读出后,经过VGA时序模块和HDMI发送模块后输出显示器,代码位置如下:

VGA时序配置为1920X1080,HDMI发送模块采用verilog代码手写,可以用于FPGA的HDMI发送应用,关于这个模块,请参考我之前的博客,博客地址:点击直接前往

5、vivado工程1–>2路SFP传输

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:HDMI或者动态彩条,分辨率1920x1080@60Hz;

输出:HDMI显示器;

应用:2路SFP光口GTX aurora 8b/10b编解码视频传输;

工程Block Design如下:

工程代码架构如下:

综合编译完成后的FPGA资源消耗和功耗预估如下:

6、vivado工程2–>1路SFP传输

开发板FPGA型号:Xilinx–Kintex7–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:HDMI或者动态彩条,分辨率1920x1080@60Hz;

输出:HDMI显示器;

应用:1路SFP光口GTP aurora 8b/10b编解码视频传输;

工程Block Design如下:

工程代码架构如下:

综合编译完成后的FPGA资源消耗和功耗预估如下:

7、上板调试验证

光纤连接

工程1:2路SFP传输的光纤接法如下:

工程2:1路SFP传输的光纤接法如下:

静态演示

下面以工程1:2路SFP传输为例展示HDMI输入后的输出效果:

当GTX运行5.94G线速率时输出如下:

下面以工程1:2路SFP传输为例展示动态彩条输出效果:

当GTX运行5.94G线速率时输出如下:

动态演示

下面以工程1:2路SFP传输为例展示HDMI输入后的输出效果演示视频:

K7-GTX-HDMI-LOOP

下面以工程1:2路SFP传输为例展示动态彩条输出效果演示视频:

K7-GTX-HDMI-COLOR文章来源:https://www.toymoban.com/news/detail-684639.html

8、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: 文章来源地址https://www.toymoban.com/news/detail-684639.html

文章来源地址https://www.toymoban.com/news/detail-684639.html

到了这里,关于FPGA GTX全网最细讲解,aurora 8b/10b协议,HDMI视频传输,提供2套工程源码和技术支持的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!