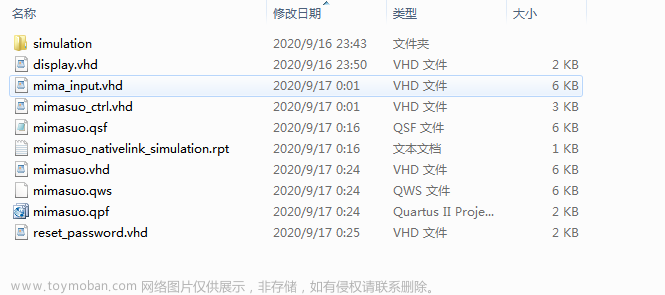

当VHDL模块中有Generic块时,应该怎么例化?

VHDL模块代码文章来源:https://www.toymoban.com/news/detail-685314.html

entity GenericExample is

generic (

DATA_WIDTH : positive := 8; -- 泛型参数:数据宽度

ENABLE_FEATURE : boolean := true -- 泛型参数:是否启用特定功能

);

Port (

clk : in STD_LOGIC;

reset : in STD_LOGIC;

data_in : in STD_LOGIC_VECTOR(DATA_WIDTH - 1 downto 0);

data_out : out STD_LOGIC_VECTOR(DATA_WIDTH - 1 downto 0)

);

end GenericExample;

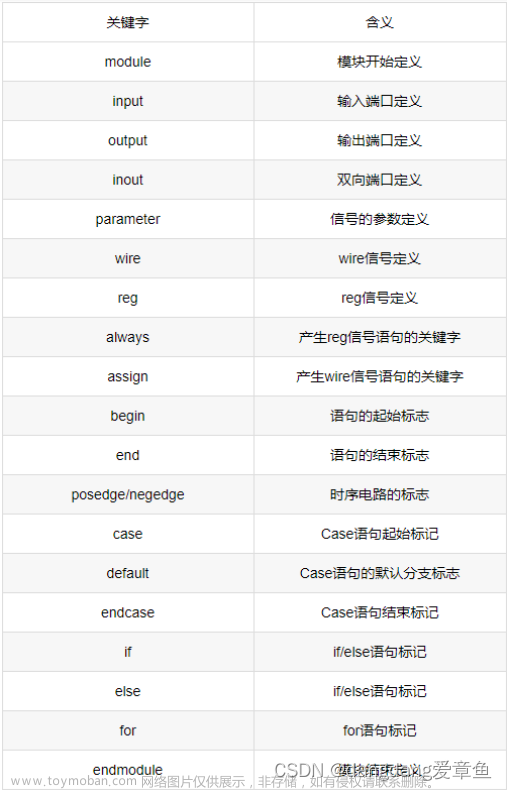

Verilog仿真代码文章来源地址https://www.toymoban.com/news/detail-685314.html

// 实例化泛型实体

GenericExample

#(

.DATA_WIDTH (8 ), // 设置数据宽度为8

.ENABLE_FEATURE (1 ) // 启用特定功能

)

UUT(

.clk (clk ),

.reset (reset ),

.data_in (data_in ),

.data_out (data_out )

);

到了这里,关于FPGA | Verilog仿真VHDL文件的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!