推荐查看原文:硬件电路设计之eMMC电路设计eMMC(Embedded Multi Media Card)是嵌入式多媒体卡的简称,主要是针对智能手机和平板电脑特点等设计的。它的实质是在NAND Flash的基础上增加了一个控制器,并预留了一个标准接口。https://mp.weixin.qq.com/s/c9osuOX-XvQYD6lz-3L2ew

注意:原文的内容更加全面。

1 简介

eMMC(Embedded Multi Media Card)是嵌入式多媒体卡的简称,主要是针对只能手机和平板电脑特点二设计的。它的实质是在NAND Flash的基础上增加了一个控制器,并预留了一个标准接口。

2 免费资料获取

参考设计获取方式:关注下面公众号,回复:eMMC即可。

3 引脚功能描述

eMMC颗粒的PIN脚主要分为三组:电源引脚、控制信号引脚、数据信号引脚。

-

电源引脚

VCCQ电压:该电压由CPU的数据总线的VCCIO决定(eMMC总线VCCIO值必须与VCCQ保持一致)

VCC电压:该电压为核心电压;

VDDIM:内部与内核供电端相连,主要功能是稳定内核电压,该PIN脚直接连接一个对地的1μF电容。

-

控制信号引脚

CLK:从Host输出的时钟信号,用于数据的同步。

CMD:主要用于Host向eMMC发送指令以及eMMC向Host发送请求。

DS时钟:DS时钟由eMMC发送给Host,用于Host与eMMC进行数据接收同步。只有在HS400模式下,才需要使用DS引脚。

注意:HS200模式下,需要使用CLK、CMD、D[3...0];HS400模式下,需要使用CLK、CMD、D[7...0]、DS。

-

数据信号引脚

D[7...0]:Dx信号主要用于 Host 和 eMMC 之间的数据传输。在 eMMC 上电或者软复位后,只有 DAT0 可以进行数据传输,完成初始化后,可配置 4bit 或者8bit进行数据传输。

4 eMMC封装

针对eMMC的封装,根据PIN脚可以分为153ball和169ball,但是这两种的引脚是兼容的,知识后者多了16个空脚,用于芯片的固定,没有任何信号定义。芯片封装万科的尺寸由:

-

11.5*13

-

12*16

-

14*18

-

16*20

实物如下:

通常,我们在PCB Layout时,会预留最大的尺寸,焊盘会绘制成169ball,这样可以兼容153ball的芯片。

5 硬件电路设计

-

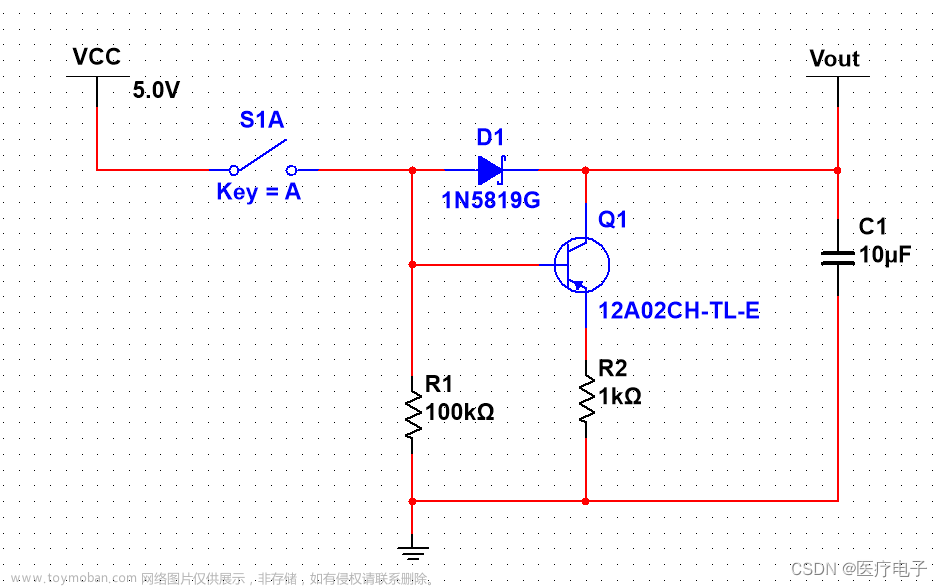

电源部分电路

-

控制和数据引脚文章来源:https://www.toymoban.com/news/detail-689555.html

-

其他部分文章来源地址https://www.toymoban.com/news/detail-689555.html

到了这里,关于数字电路硬件设计系列(十八)之eMMC电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!