前言

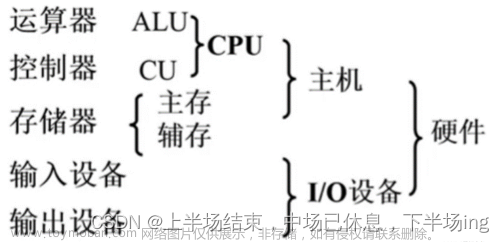

随着人工智能的发展以及大部分场景中实时性的要求,人们对于计算机算力要求逐渐增加。为了提高计算速度,计算平台从单核发展为多核,从标量数据发展为向量化运算,进而发展到当下流行的异构并行计算。

异构,是指计算硬件平台由不同架构的处理器组成,如CPU+GPU、CPU+FPGA、CPU+DSP,甚至是CPU+GPU+FPGA。异构相当于使用了一个具有多处理器的计算平台,博众家之长,以获得优异的算力,加快任务的处理速度。其中CPU擅长调度,GPU擅长向量运算,DSP擅长数字信号处理,FPGA则利于用户自定义配置。

并行,是发挥异构平台效能所必须采用的运行方式,它包含两个含义:一是不同架构的处理器需要同时计算,避免闲置;二是每个处理器一般都是多核向量处理器,需要使用并行编程以充分发挥处理器的计算能力。

所以,“异构并行”是一个不可分割的词组。

OpenCL(Open Computing Language)就是在异构并行计算发展的道路上,兴起的一种编程语言模型,由于其开源性和高度通用的跨平台设计原则,得到了多家处理器大厂的支持,包括AMD、Intel、Altera等。

本文对异构并行计算的起源、及OpenCL的出现进行介绍,方便大家进一步体会设计师在算力提升道路上的努力。

参考:《OpenCL异构并行计算——原理、机制与优化实践》

一、单核标量处理器的瓶颈

在2005年前,大部分处理器都是单核的,并且大部分的应用程序只使用了单核处理器的标量性能,即在同一时间内只处理一个数据(整数或浮点数),称为SISD(单指令单数据流)。基于CISC、RISC指令集设计的处理器即属于SISD类。

对于单核标量处理器而言,性能提升只能从以下两个方面入手,

- 提升处理器的时钟频率

- 提升指令级并行能力

然而,两条路都会遇到发展瓶颈。 摩尔定律称 “单核标量处理器性能每18个月提升一倍”,这条定律在2005年之后就不灵了==

1.提升时钟频率

处理器的时钟频率表示处理器1秒内可以运行多少个基本操作,每个基本操作需要占用一个时钟周期。一些复杂的操作则需要占用几个时钟周期,而一条指令包含了多个基本/复杂操作。当我们提升处理器的时钟频率时,1秒内处理器就可以执行更多的操作,也就能加快指令的执行速度,从而增加了算力。

一般情况下,能显著提高处理器时钟频率的方法是减小芯片制程。

这里解释一下为什么制程影响时钟频率。处理器芯片绝大多数属于数字逻辑芯片,其主要组成是大量的晶体管,芯片制程指晶体管栅极的最小宽度(即常说的7nm、14nm…)。当制程越小时,电流通过栅极的速度越快,晶体管的翻转速度就越快,也就可以支持较大的时钟频率。

我们常说的超频则是指使CPU在超过其额定时钟频率下工作,这可能导致晶体管的状态来不及变化,产生死锁或丢数等故障。

减小芯片制程,在提高时钟频率的同时,还能减小晶体管体积,使得芯片上可以布下更多的晶体管,进一步提升算力。

但更高的时钟频率也带来了更多的功耗(主要是漏电功耗),大致来说处理器的功耗和处理器频率的三次方近似成正比。功耗带来热量,处理器的频率增大的同时,散热也在增多。在处理器的散热达到现实环境、技术能够满足的界限时,无法再增加频率,否则处理器会烧毁。

因此,功耗限制了时钟频率的提升!

2.提升指令级并行能力

处理器在执行指令时可分为五个步骤:取指令、指令解码、执行、访存和写回

为了增大数据吞吐量,处理器会采用流水线的方式执行指令,流水线工作原理可参考:

【计算机组成原理】流水线式指令执行

由于指令中存在分支判断、数据依赖等情况,因此流水线的执行有很大优化空间,尤其需要编译器在编译源码时充分考虑代码运行特点,合理安排流水线,以生成较优的执行文件。

但是要利用好指令级并行能力,对于代码优化人员、编译器作者和处理器设计师都有很高的要求。他们采取的优化方式包括合理重用寄存器、增加硬件流水线层级等。

目前,提升指令级并行能力也达到了一定局限性。

二、多核和向量化

1.多核

前面讲过,在单核上不断提高时钟频率以谋求更高的计算性能,会使得功耗越来越大,芯片难以承受。但换一种思路,为何非要单打独斗呢?

因此多核出场了,在一个芯片上使用多个核心共同计算,可以起到“三个臭皮匠顶个诸葛亮”的效果。

并且,多核支持了多线程并行,每个核都可以运行一个任务,计算机可以同时处理用户的不同请求,提高使用体验。

2.向量化

向量化是指一条指令同时处理多个数据,是一种数据并行技术。

主流的向量化技术包括:单指令多数据(SIMD),单指令多线程(SIMT)

由于SIMD依赖于更多的处理器ALU,而SIMT依赖于多核,因此多数CPU采用SIMD技术,多数GPU采用SIMT技术。二者的具体介绍可参考:怎么理解SIMD和SIMT

若把标量运算看作是指令对一个数字进行操作,那么SIMD可以理解为指令对一个向量进行操作。一个向量中包含多个数字,因此一次指令的执行就可以获得多个数字的计算结果,相比于原来只能获得一个计算结果来说,SIMD提高了计算效率。可视化如下图

多核和向量化能大幅提升代码性能,但是需要程序员对代码进行并行化,需要分析代码中数据和操作的依赖关系,处理任务和数据的划分。

重要的是,若代码无法多核并行化或向量化,那么多核向量处理器的一些算力就会浪费。

三、异构并行和OpenCL

异构并行的概念在前言部分已做过介绍,那么它相对于多核向量化的优势是什么呢?

我认为,异构并行汇聚了各类处理器的优势,可以允许程序员灵活配置代码的运行平台。无法并行的代码就在CPU上运行,而大量数据的并行运算则可以放在GPU上执行,充分发挥综合平台的优势,实现代码运行的最大性能。

异构平台也存在功耗大的问题,此时功耗和性能就是一对需要权衡的特性,设计人员要自我把控。

提到异构平台,不得不提到的就是GPU的发展,它的强大算力成为异构并行设计的重要支撑。

1.GPGPU

GPU(Graphics Processing Unit),顾名思义,是图形处理器,设计之初是专门用来渲染图形界面的。它的每个部件都是为了图形渲染的某一个阶段特殊设计的。渲染一个图形需要顺序地经过所有流水线处理。

在当时,若要使用GPU进行计算,就必须将算法映射成图形的渲染过程,用来进行图形编程的主要接口就是OpenGL。使用OpenGL可以将计算过程映射为图形渲染过程,进而达到计算目的。这样的GPU称为GPGPU。

这无疑对程序员的图形渲染知识要求很高,因此后续出现了更适于计算的GPU。2007年NVIDIA推出GTX8800,采用了统一的渲染架构,这使得通用计算更容易进行。

2.CUDA和OpenCL

CUDA是NVIDIA推出的通用并行计算架构,配套自家的GPU平台使用,开发者使用C语言即可基于该架构进行并行计算,调动多核GPU的强大算力。CUDA仅支持NVIDIA的GPU,通用性不高;开源的OpenCL架构成为处理器厂商青睐的对象,也因此具有较高的通用性。

OpenCL由苹果公司开发,后期交给Khronos Group维护,当前已经更新至OpenCL 3.0版本。它支持包括GPU、CPU在内的多种处理平台,并且主流或新起的处理器厂家也更倾向于选择OpenCL作为自己的并行计算架构。

OpenCL提供主机端API,有自己的硬件架构,提供完整的并行编程框架,对于开发者而言也是比较友好的。文章来源:https://www.toymoban.com/news/detail-689959.html

【博客参考】

CPU时钟周期和时钟频率文章来源地址https://www.toymoban.com/news/detail-689959.html

到了这里,关于【OpenCL基础 · 一】因源的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!