问题背景

在学习FSMC控制外部NOR存储器时,看到在NOR复用接口模式下,AD信号[15:0]是复用的。也就是说,若不使用锁存器:当NADV为低时,ADx(x=0…15)上出现地址信号Ax,当NADV变高时,ADx上出现数据信号Dx。若使用锁存器:可同时在ADx上得到Ax和Dx。

复用模式:低16位数据/地址线复用。在该模式下,推荐使用地址锁存器以区分数据与地址。

NADV信号的高低决定数据是data还是address,这个很好理解。

那么啥是锁存器,为什么使用了锁存器就可以同时得到Ax.?

简介

以锁存器—74HC573D为例

真值表

74HC573芯片是一个锁存器简单来说就是由输入引脚 D1~D8 来控制输出引脚 Q1 ~ Q8。OE和LE 的取值会影响 输入数据 控制 输出数据 。

OE:output enable 输出使能(低电平有效)

LE:latch enable 锁存器使能文章来源:https://www.toymoban.com/news/detail-695071.html

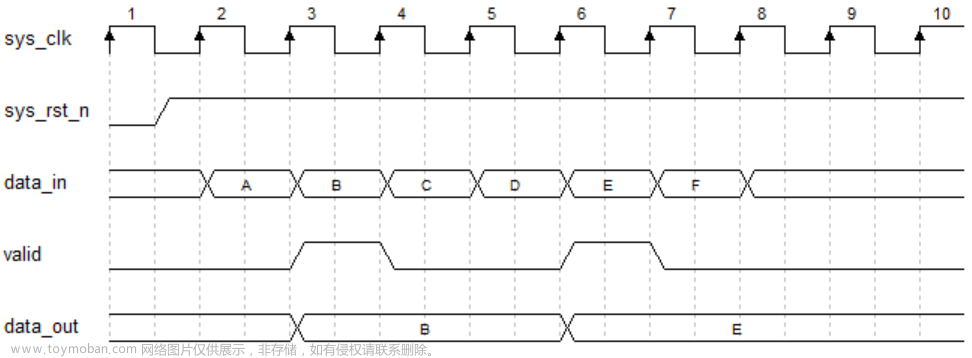

当 OE 为 L ,LE 为 H 时,为 跟随模式,输出数据 = 输入数据 。

当 OE 为 L ,LE 为 L 时,为 锁存模式,输出数据 = 上一个时刻的输入数据 。文章来源地址https://www.toymoban.com/news/detail-695071.html

到了这里,关于【STM32】锁存器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!