本文介绍使用KC705开发板进行MGT的IBERT测试。

KC705开发板

KC705开发板的图片如下图所示。FPGA芯片型号为XC7K325T-2FFG900C。

MGT

MGT是 Multi-Gigabit Transceiver的缩写,是Multi-Gigabit Serializer/Deserializer (SERDES)的别称。MGT包含GTP、GTX、GTH、GTZ、GTY、GTM。在Kintex-7系列FPGA只有GTX。

根据UG810中介绍,KC705上引出的16个GTX收发器分别是

- Eight of the GTX transceivers are wired to the PCI Express® x8 endpoint edge connector (P1) fingers

- Four of the GTX transceivers are wired to the FMC HPC connector (J22)

- One GTX is wired to the FMC LPC connector (J2)

- One GTX is wired to SMA connectors (RX: J17, J18 TX: J19, J20)

- One GTX is wired to the SFP/SFP+ Module connector (P5)

- One GTX is used for the SGMII connection to the Ethernet PHY (U37)

7系列FPGA中的GTX收发器分为四个通道,称为Quad。某Quad的参考时钟可以来源于上一个Quad或下一个Quad。KC705板上有4个GTX Quad,具体连接如下表所示:

| Transceiver Bank | Associated Net Name | Connections |

|---|---|---|

| MGT_BANK_115 | GTXE2_CHANNEL_X0Y0 | PCIe7 |

| GTXE2_CHANNEL_X0Y1 | PCIe6 | |

| GTXE2_CHANNEL_X0Y2 | PCIe5 | |

| GTXE2_CHANNEL_X0Y3 | PCIe4 | |

| MGTREFCLK0 | N/C | |

| MGTREFCLK1 | PCIe_CLK | |

| MGT_BANK_116 | GTXE2_CHANNEL_X0Y4 | PCIe3 |

| GTXE2_CHANNEL_X0Y5 | PCIe2 | |

| GTXE2_CHANNEL_X0Y6 | PCIe1 | |

| GTXE2_CHANNEL_X0Y7 | PCIe0 | |

| MGTREFCLK0 | Si5326 | |

| MGTREFCLK1 | FMC LPC GBT_CLK0 | |

| MGT_BANK_117 | GTXE2_CHANNEL_X0Y8 | SMA |

| GTXE2_CHANNEL_X0Y9 | SGMII | |

| GTXE2_CHANNEL_X0Y10 | SFP/SFP+ | |

| GTXE2_CHANNEL_X0Y11 | FMC LPC DP0 | |

| MGTREFCLK0 | SGMII_CLK | |

| MGTREFCLK1 | SMA_CLK | |

| MGT_BANK_118 | GTXE2_CHANNEL_X0Y12 | FMC HPC DP0 |

| GTXE2_CHANNEL_X0Y13 | FMC HPC DP1 | |

| GTXE2_CHANNEL_X0Y14 | FMC HPC DP2 | |

| GTXE2_CHANNEL_X0Y15 | FMC HPC DP3 | |

| MGTREFCLK0 | FMC HPC GBT_CLK0 | |

| MGTREFCLK1 | FMC HPC GBT_CLK1 |

时钟

KC705板载的时钟源有以下几个

1. System Clock Source

系统时钟源为2.5V LVDS差分200 MHz振荡器,SYSCLK_P——AD12,SYSCLK_N——AD11。

2. Programmable User Clock Source

可编程用户时钟源为低抖动3.3V差分振荡器Si570,USER_CLOCK_P——K28, USER_CLOCK_N——K29。上电默认输出频率为156.250 MHz,可通过I2C接口在10MHz~810 MHz范围内调整输出频率。

3. User SMA Clock Input

连接关系:

USER_SMA_CLOCK_P ——L25,USER_SMA_CLOCK_N——K25。

4. GTX SMA Clock Input

连接关系:

SMA_MGT_REFCLK_P——J8,SMA_REFCLK_N——J7,其连接至Bank 117 MGT参考时钟1。

5. Jitter Attenuated Clock

连接关系:

REC_CLOCK_C_P——W27,REC_CLOCK_C_N——W28。

SI5326_OUT_C_P——L8,SI5326_OUT_C_N——L7,连接至Bank 116 MGT参考时钟0。

SI5326_RST——SI5326_RST_LS——AE20。

6. SGMII GTX Transceiver Clock

ICS844021I为一个倍频系数固定为5的芯片,故在此处其输出为125 MHz LVDS差分时钟。

连接关系:SGMIICLK_Q0_P——G8,SGMIICLK_Q0_N——G7,连接至Bank 117 MGT参考时钟0。

IBERT IP核

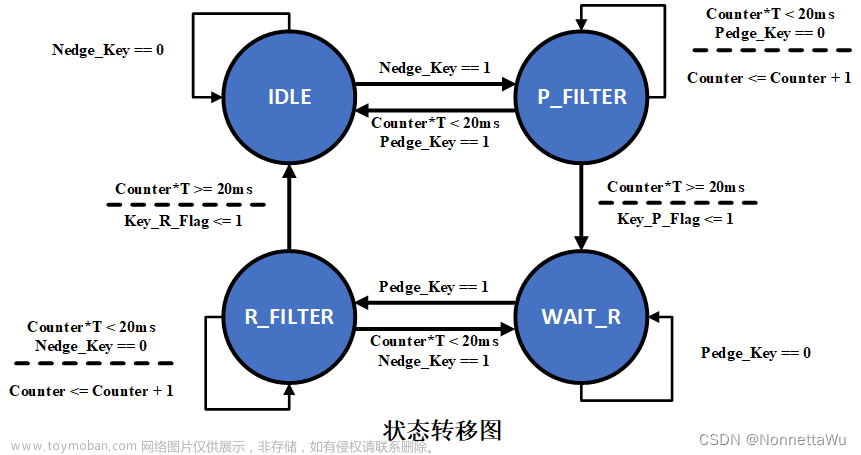

Protocol Definition

在Protocol为Custom1时,线速率LineRate、数据位宽DataWidth、参考时钟频率Refclk可自行指定。Quad Count取决于待测试的GTX是否位于同一个Bank。勾选Quad PLL则该Quad内的GTX共用一个QPLL,不勾选则不同GTX使用不同的CPLL。QPLL和CPLL的关系示意图如下。

Protocol Selection

根据待测试的GT所位于的Bank号设置Protocol Selected。参考时钟Refclk可以来自于本Quad或上一个Quad或下一个Quad的参考时钟输入。在前面勾选Quad PLL的情况下,TXUSERCLK Source可以任意设置。

Clock Settings

系统时钟System Clock可以选择前面所设置的GT参考时钟,也可以选择外部参考时钟。

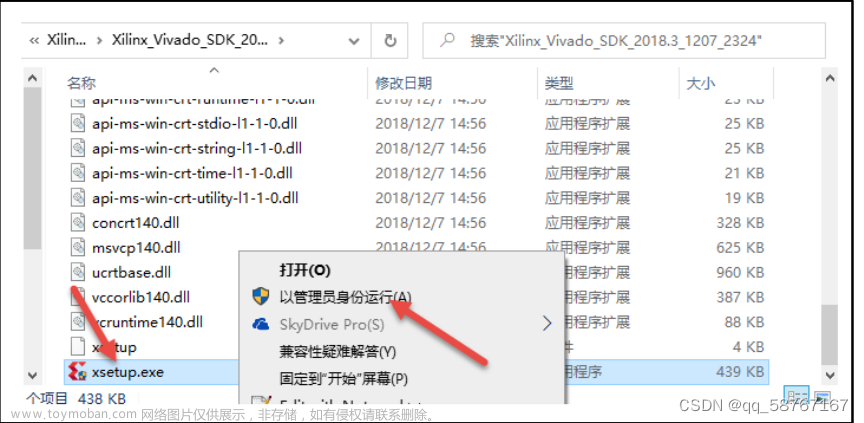

生成IP核示例工程

右击IP核后,点击Open IP Example Design生成工程。

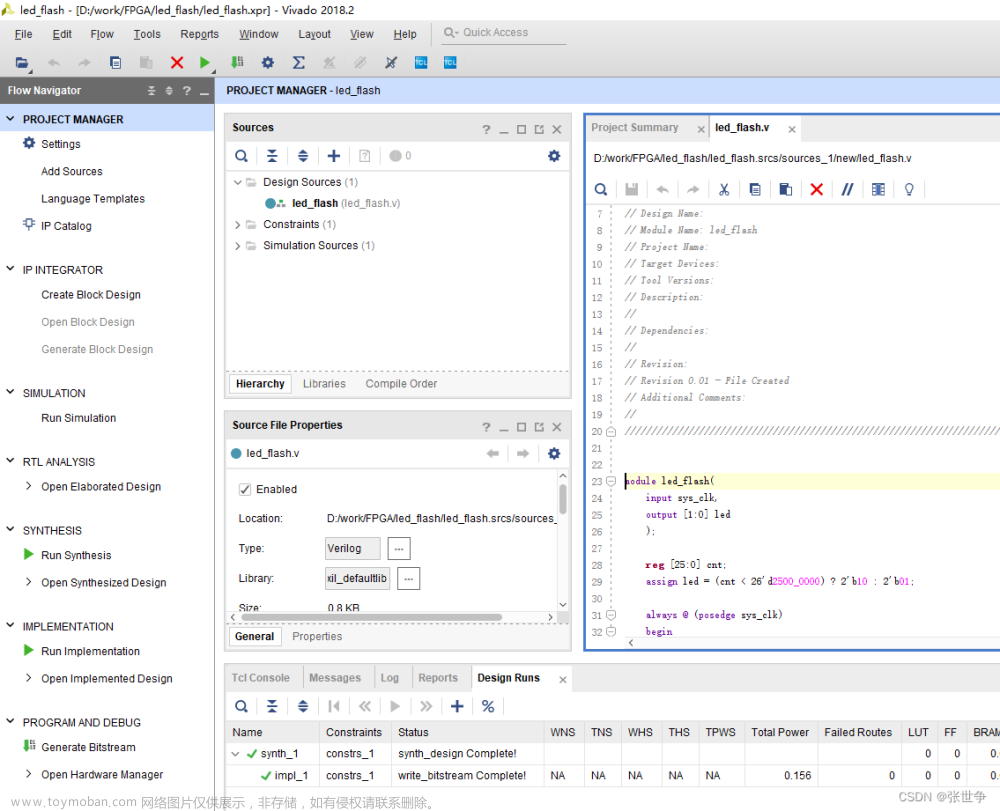

注意事项

生成IP核示例工程后,查看综合后的Schematic和I/O Ports确认。

此时修改该工程中的IBERT IP核的GT参考时钟和系统时钟时,引脚分配是不会发生改变的。

SMA回环测试

根据前面的介绍,接下来进行KC705的GT测试。KC705上的J17和J66、J19和J20分别连接了Quad 117的GT的接收通道和发送通道。使用SMA连接线将J17与J19相连,J66与J20相连。

生成并下载Bitstream,点击Auto-detect links,即可看到测试结果。

链路测试所用的回环方式一共有4种,分别是

该4种方式在通信链路中对应的位置示意图如下。

点击Serial I/O Scans中的Create Scan创建扫描。

扫描后得到如下结果。

SFP+回环测试

使用如图所示的回环器,插到KC705开发板上的SFP/SFP+连接器上。

Bank 117上GT收发器的连接关系如下表。

| Transceiver Bank | Associated Net Name | Connections |

|---|---|---|

| MGT_BANK_117 | GTXE2_CHANNEL_X0Y8 | SMA |

| GTXE2_CHANNEL_X0Y9 | SGMII | |

| GTXE2_CHANNEL_X0Y10 | SFP/SFP+ | |

| GTXE2_CHANNEL_X0Y11 | FMC LPC DP0 | |

| MGTREFCLK0 | SGMII_CLK | |

| MGTREFCLK1 | SMA_CLK |

注意到SPF/SFP+所连接的GT收发器是X0Y10,参考时钟输入1来自于外部时钟输入。

此时IBERT IP核参考时钟,仍可选择SMA回环测试中的MGTREFCLK0 117。为了再做一个MGT参考时钟的实验,将参考时钟设为MGTREFCLK1 117。时钟产生方法是从其他博主那里学到的。

即是将SI570默认输出的156.250MHz的差分时钟输入(引脚为K28和K29);

通过USER_SMA_CLOCK(引脚为L25和K25,SMA头为J11和J12)输出;

然后通过SMA连接线接到SMA_MGT_REFCLK(Bank 117的参考时钟1,引脚为J8和J7,SMA头为J16和J15)。

最后的硬件连接关系如下图所示。

此时需要更改IBERT IP核中GTX的参考时钟频率和来源,同时该SFP+回环器最高支持10 Gbps,于是我们也将线速率设置为10 Gbps。具体设置如下图所示。

接下来,重新生成IBERT IP核示例工程。

在示例工程的顶层文件中,添加如下代码。

input USER_CLOCK_P;

input USER_CLOCK_N;

output USER_SMA_CLOCK_P;

output USER_SMA_CLOCK_N;

wire user_clock;

IBUFGDS u_user_clock

(

.I(USER_CLOCK_P),

.IB(USER_CLOCK_N),

.O(user_clock)

);

wire user_clock_bufg;

BUFG u_BUFG_sysclk (

.O(user_clock_bufg),

.I(user_clock)

);

OBUFDS u_OBUFDS_sysclk (

.O (USER_SMA_CLOCK_P),

.OB(USER_SMA_CLOCK_N),

.I (user_clock_bufg)

);

同时在xdc文件中,添加时钟约束和引脚约束。

create_clock -name user_clock -period 6.4 [get_ports USER_CLOCK_P]

create_clock -name user_sma_clock -period 6.4 [get_ports USER_SMA_CLOCK_P]

set_property PACKAGE_PIN K28 [get_ports USER_CLOCK_P]

set_property IOSTANDARD LVDS_25 [get_ports USER_CLOCK_P]

set_property PACKAGE_PIN L25 [get_ports USER_SMA_CLOCK_P]

set_property IOSTANDARD LVDS_25 [get_ports USER_SMA_CLOCK_P]

综合后得到额外的RTL电路为。 文章来源:https://www.toymoban.com/news/detail-695157.html

文章来源:https://www.toymoban.com/news/detail-695157.html

生成并下载Bitstream,链路正常锁定,得到链路测试结果如下。

眼图扫描结果如下。 文章来源地址https://www.toymoban.com/news/detail-695157.html

文章来源地址https://www.toymoban.com/news/detail-695157.html

参考资料

- kc705_Schematic_xtp132_rev1_1.pdf

- xtp200-kc705-ibert-c-2014-3.pdf

- ug810_KC705_Eval_Bd.pdf

- ug811_ChipScopeUsingIBERTwithAnalyzer.pdf

到了这里,关于KC705开发板——MGT IBERT测试记录的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!