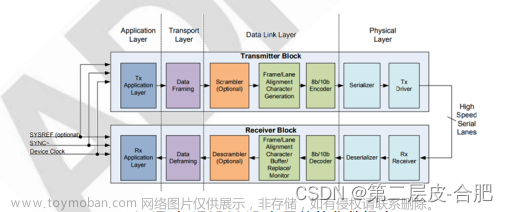

挑战

随着器件开关速度的不断提高,保持信号完整性和满足信号时序要求的挑战也随之而来。信号完整性可通过受控阻抗布线进行管理,为此需要仔细设计PCB堆栈和每层上使用的布线宽度。

通过匹配信号路径的布线长度,满足时序要求。对于一组2个引脚的信号路径,每条路径均将从输出引脚运行至输入引脚,因此仅需计算和对比其长度。但就许多典型设计方案而言,情况并非如此,因为信号路径中可能有一个串联终端元件,或者信号中有两个以上的引脚,此时可以使用Balanced T或Fly-By布线拓扑结构进行布线,如下图所示。

用Balanced T拓扑结构对四个DDR2 RAM芯片进行布线。

解决方案

设计者的任务是将设计要求(例如,为满足时序预估而允许的最大布线长度)转化为一组设计规则(例如,确保满足时序的Length规则,以及检测潜在时序不匹配的Matched Length规则)。

设计者此时将根据信号功能理解信号(例如,“必须将该地址信号从该连接器布线至每个存储设备。为此,我将使用一个终端电阻位于末端的Fly-by拓扑结构。我可能还需要在源头处安装一个串联终接器”)。即使地址A0通过了终端电阻,但对设计者而言,该信号在该电阻另一侧仍然是A0。

但PCB编辑器仅将每个信号简单视为一组相互连接的引脚(通称为网络)——网络A0将从连接器引脚延伸至某个存储元件引脚,然后延伸至另一个存储元件引脚,以此类推。在添加一个串联终端电阻后,该地址线将立即变为两个离散网络。这样将使得设计者难以具体说明关键设计要求(例如,Length和Matched Length设计规则)。

我们可以使用xSignals功能对其进行管理。我们可以使用该功能通过终端元件以及分支,正确处理高速信号路径——在信号源于目的地之间的信号路径。

xSignal本质上是设计者定义的两个节点之间的信号路径。该节点既可以是同一网络内的两个节点,亦可以是由元件隔开的相关网络内的两个节点。我们可以使用xSignal确定相关设计规则(例如,Length和Matched Length)的范围,并在以后执行设计任务过程(例如,进行交互式长度调整)中遵守这些规则。

创建新xSignal

xSignal是两个节点之间的设计者自定义信号路径;它们既可以是同一网络内的两个节点,亦可以是不同网络内的两个节点。

xSignal可以使用以下方法进行定义:

使用xSignals Multi-Chip Wizard。该方法是创建xSignals的最常用方法,我们将在xSignals Multi-Chip Wizard页面上详细介绍。

还可以通过在选中相关对象后,选择适当命令,使用以下方法:

根据选中的焊盘,创建一个单一xSignal。选中所需的起始焊盘和终止焊盘(如果有串联终端元件,则这些焊盘可以在不同网络中)。焊盘既可以在设计空间中直接选中,亦可以在Nets模式下使用PCB面板进行定位和选中(如下图所示)。选中焊盘后,即可以在设计空间中右键单击选中的焊盘,然后运行xSignals » Create xSignal from Selected Pins命令,或者在PCB面板中右键单击其中一个选中的焊盘,然后运行Create xSignal命令。新xSignal将在PCB面板的xSignals模式中列出。

当您根据选中的引脚(封装焊盘)定义一个xSignal时,应在运行Create命令前,仅选中起始焊盘和终止焊盘。

新xSignal的名称将由两个网络名称组合而成,并用连字符分开。xSignal的名称可以在PCB面板的xSignals模式中进行编辑。

可在面板的xSignal Classes区域右键单击,创建一个新类并向其添加成员,以将新xSignal添加到xSignal类中。

选中源元件,然后右键单击所选元件,并选择上下文菜单中的xSignal » Create xSignals between Components命令。Create xSignals Between Components对话框将打开,所选源元件将被选中。该对话框具体如下。

在设计空间中选中一个或多个串联元件,然后右键单击其中一个选中的元件,并从上下文菜单中选择xSignal » Create xSignals from Connected Nets命令。Create xSignals From Connected Nets对话框将打开。所选源元件以及与该元件连接的网络均将被选中。该对话框具体如下具体如下。

如果您想在现有xSignal中创建一个xSignal,则可以使用PCB面板的xSignal模式。请确保已启用面板顶部的Select选项,找到当前xSignal,在面板的xSignal Primitives部分选中所需焊盘,然后在设计空间中右键单击其中一个选中的焊盘,并使用本列表步骤2中所描述的方法完成创建过程。

在面板的Nets模式中选中两个焊盘,右键单击其中一个选中的焊盘,然后选择Create xSignal。请注意,这些焊盘位于不同网络。

Create xSignals Between Components对话框

如果有大量xSignals需要定义,则使用Create xSignals Between Components对话框将更加有效。可通过Design » xSignals » Create xSignals命令访问该对话框,且该对话框将显示Source Components及其Source Component Nets和Destination Components,并允许您在一次操作中创建一个或许多xSignals。方法是:

使用对话框快速识别和创建多个xSignal,并将它们添加到所需的xSignal类中。

方法为:

选中一个单一源元件。

选中一个或多个需要的目标元件。

选中相关Source Net。目前与所选源元件相连的所有网络均将被列出。对于与特定类相关的网络,请在Net Class下拉菜单中选择该类。

单击Analyze按钮。 该软件将尝试识别所选网络的源元件与目的元件之间存在的潜在xSignals。包含所选网络且在所选源元件与目的元件之间运行的所有潜在xSignals,均将被列在xSignals字段。请注意,分析算法将遵循所选网络的当前拓扑结构,从而影响建议的xSignals。

必要时,该软件还可以通过在Analyze下拉菜单中选中适当的选项,搜索串联元件:搜索直接连接、Through 1串联元件、Through 2串联元件或Multipath耦合网络。

分析完成后,潜在xSignals将被列在对话框的下部区域,且所有xSignals均将被启用,以完成创建。请仔细检查拟议xSignals列表,且仅启用需要的xSignals。 使用右键单击上下文菜单中的可用命令,在多个入口之间进行切换。

在对话框底部选择所需类,或输入一个名称,以创建一个新类。即使未选择任何类,xSignals仍然被创建,并且您可以在Object Class Explorer对话框(Design » Classes)中将其添加到任何xSignal类。 使用类可以显著简化设计规则的创建和配置。

点击OK,以创建xSignals。

对话框将关闭,并返回到设计空间。新xSignals将被列在PCB面板的xSignals模式中。

使用各列表上方的过滤器,快速定位相关元件或网络;支持通配符。

Create xSignals From Connected Nets对话框

如果您正在创建包含串联终端元件的xSignals,则最好使用Create xSignals from connected nets命令。仅需通过主菜单中的Design » xSignals子菜单或右键单击xSignals子菜单选中元件,即可使用该命令。

该命令旨在从选中的串联终端元件(例如,电阻或电容)由内而外创建xSignals。其既支持一个或多个离散元件,亦支持一个或多个多实例包样式元件(例如,电阻网络)。运行此命令后,Create xSignals From Connected Nets对话框将打开。

使用该对话框,创建跨越选中串联元件的xSignals。在该示例中,提出了两个可能的xSignals,但仅创建一个。

其方法是:

选中一个单一源元件。

选中相关Source Net。目前与所选源元件相连的所有网络均将被列出。对于与特定类相关的网络,请在Net Class下拉菜单中选择该类。

单击Analyze按钮。该软件将尝试识别所选源元件和所选网络中存在的潜在xSignals。所有潜在xSignals均将被列在xSignals字段中。

完成分析后,潜在xSignals均将被列在对话框的下部区域,且所有xSignals均将被启用以进行创建。请仔细检查建议的xSignals列表,且仅启用需要的xSignals。使用右键单击上下文菜单中的可用命令,在多个入口之间进行切换。

在对话框底部选中所需类,或者输入名称以创建一个新类。即使未选择任何类,xSignals仍将被创建,且您可以在Object Class Explorer对话框(Design » Classes)中,将其添加到任何xSignal类中。使用类可以显著简化设计规则的创建和配置。

单击OK以创建xSignals。

该对话框将关闭,并返回设计空间。新xSignals将被列在PCB面板的xSignals模式中。

使用各个列表上方的过滤器,快速定位相关元件或网络;支持通配符。

网络拓扑结构的作用

当您定义某个xSignal时,其将出现在两个节点或焊盘之间。但当您在PCB面板的xSignals模式下选中该xSignal时,其实际将以这两个焊盘之间的连接线为路径运行,表明该路径为软件假设该xSignal将被布线的路径。软件之所以这样假设,是因为其遵守针对该网络定义的拓扑结构。网络拓扑结构将按照相关布线拓扑设计规则进行定义;默认拓扑结构为Shortest。

该简单动画所示为一个与四个DDR3内存芯片相连的CPU,其中该CPU将按照Fly-by布线策略进行布线。DRAM_A2 xSignal类包含四个xSignal。首先,选中该类,然后依次选中每个xSignal。您可以看到xSignal的路径是如何遵循网络拓扑结构的,且其目前被设置为默认拓扑结构——即,Shortest。

由于网络拓扑结构目前已被设置为Shortest,因此xSignal未遵循从处理器到内存芯片的必要路径。

如果打算使用Create xSignals Between Components对话框,则需要配置网络拓扑结构,以确保xSignal分析算法理解布线xSignal的预期路径。

xSignal创建命令

除Design » xSignals » Create xSignals命令外,还可以在满足某些条件的情况下,使用xSignals子菜单中的其他xSignal创建命令。

以下内容总结了相关命令以及何时可以使用这些命令:

指令 描述

Create xSignal from selected pins 立即创建一个 xSignal。当在设计空间中选择了两个或更多焊 盘 时,此命令可用,并且与您右键单击所选焊盘之一时显示的命令相同。

Create xSignals between components 当在设计空间中选择元件时,此命令可用。当它运行时,Create xSignals Between Components 对话框打开,其中包含预选的元件。确保选择了正确的来源和目标元件,然后完成分析/创建过程。

Create xSignals from connected nets 当有一个或多个串联终端元件要为其创建 xSignals 时使用此命令。选择终端元件,然后运行命令打开 Create xSignals from Connected Nets 对话框,准备完成创建一组 xSignals 的过程。

Create xSignals 打开Create xSignals Between Components对话框。此命令始终可用。

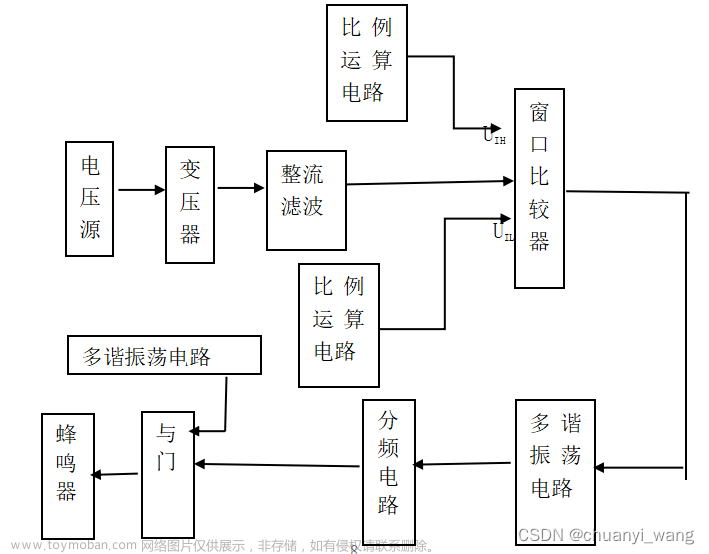

Balanced T模式中分支点的定义

Balanced T型布线策略的其中一项挑战是如何均衡T点以外主干和分支的长度。由于网络中的可用节点仅出现在焊盘上,因此不可能为主干,以及从分支点到每个分支末端单独定义xSignals。分支点在下图中用红点表示。

解决该问题的一个方法是在网络中添加一个单引脚元件。创建一个具有单一焊盘的元件,并确保该焊盘尺寸与设计中所用过孔尺寸相同。如果分支点处元件焊盘为单层,则亦可将其与盲孔或埋孔结合使用,仅需将其放在过孔的起始层或终止层,即可灵活创建布线。如果您只想在PCB上包含分支点元件,请将分支点元件的Type设置为Mechanical,以将其从BOM中排除,并防止与原理图产生同步问题。如果您想在原理图上包含分支点元件,则可以将元件Type设置为Standard(无BOM)。

Balanced T型布线可能需要在中间分支点之间匹配长度。

此时,您可以将分支点作为网络中的一个节点,针对主干、每个主要分支和每个次要分支(如需要)定义xSignals。然后,使用定义的xSignals,确定匹配长度设计规则的范围,以确保设计者能够全面控制长度匹配的精细程度。

管理xSignals

在PCB面板的xSignals模式下,其三个主要区域均会改变,以反映当前PCB设计的xSignal层次(按自上而下的顺序):

xSignal Classes

某个类中的单独 xSignals

构成一个xSignal(焊盘、线路和过孔)的单独 xSignal Primitives

xSignal Classes 区域

xSignal Classes区域列出了任何已定义的xSignal类集合或所有可用类()。

选择一个类,以在中间区域(xSignals)中查看其xSignals列表,并将其显示在PCB设计空间。

如需从现有xSignal集合中创建一个新xSignal类,则应右键单击该区域,然后从上下文菜单中选中Add Class,以打开Edit xSignal Class对话框。该对话框列出的所有可用xSignals,均可使用管理按钮将其作为成员添加到新类中或从中删除。使用Name字段,为新xSignal类定义一个合适的名称。

通过在Edit xSignal Class对话框中添加/删除xSignal成员,创建或添加到xSignal类。

还可以使用面板区域的右键上下文菜单,删除(Delete)或更改其在PCB设计空间中的可视化表现形式(例如,Change xSignal Color)。

如需了解关于类操作的更多信息,请参考 Working with Classes on a Schematic & PCB页面。

xSignals 区域

面板的中间区域将显示在以上区域内选中的xSignal Class的xSignals。

各xSignal均将默认列出以下信息:

– 该部分具有两项功能,即:

彩色背景——分配给xSignal的颜色(设计空间中代表xSignal的细线)。右键单击,以针对所有当前选中的xSignal执行Change xSignal Color操作。

可见性复选框——使用该复选框时,无论xSignal是否当前已被选中,均将始终显示。

Name – xSignal的名称。

Node Count – 该xSignal中的焊盘总数。

Routed Length – 形成布线的已放置线路和弧线段的长度之和,加上穿过过孔的垂直距离(见下文注释)。布线长度计算器不会尝试解决焊盘内部的线路段重叠或布线摆动问题。

Signal Length – 节点之间总距离的准确计算。以下注释适用于Signal Length计算:

解决焊盘内部的重叠和摆动问题。

处理使用线路和圆弧以外的对象(例如,区域或填充)创建的布线路径。

包括通过过孔的垂直距离(见下文注释)。

包括该xSignal的Total Pin/Package Length。

包括该xSignal的Un-Routed (Manhattan) Length。

不符合相关Length/Matched Length设计规则的信号长度,将显示在彩色背景上:如果信号长度过短,则显示黄色,如果信号长度过长,则显示红色。

如需了解关于如何应用Length和Matched Length设计规则的更多信息,请参考Length Tuning 部分。

Total Pin/Package Length – 该xSignal中所有焊盘的所有Pin Package Length值之和。该值即可被定义为PCB焊盘的一个属性,亦可在原理图引脚中指定。

Unrouted (Manhattan) Length – 所有未布线部分的垂直距离加水平距离(X+Y)。

Margin – 实际信号长度与相关Length/Matched Length设计规则所定义的目标信号长度之差。

在该区域内右键单击,然后使用Columns子菜单添加以下列:

Delay – 信号沿该布线传播的时间。

使用Columns子菜单显示/隐藏列。

通过过孔的垂直距离 - 信号通过过孔的垂直距离是指起始层与终止层铜层之间所有层厚(铜和电介质)的总和,加上起始层厚度的一半和终止层厚度的一半。层厚将在Layer Stack中定义。

xSignal Primitives 区域

PCB面板的第三个区域,xSignal Primitives,列出了当前选定xSignal的所有组成要素(基元)。

选中该区域的Show nodes only复选框,将基元列表限制在作为xSignal起始/终结点节点的焊盘上。在此模式下,所选中xSignal将在PCB设计空间中显示为由代表xSignal路径的细线(而不是线路)所连接的节点焊盘。

。

xSignal Primitives下部区域列出了所选中xSignal的所有要素(例如,焊盘、过孔和线路以及其相应的延迟)。

在设计空间显示xSignals

xSignals在设计空间中显示为一条细线。该细线表示xSignal所遵循的路径。细线总长度为X/Y对该xSignal信号长度的贡献值。Z或对整个信号长度的垂直贡献,已在上文讲述。

下图所示为一个差分对的xSignals。由于面板上的xSignal复选框已被启用,因此未被选中差分对成员的xSignal仍然可见。

xSignals在设计空间中以一条细线表示。由于可见性复选框已被激活,因此即使在面板中仅选中一个,该差分对内的两个xSignal仍将同时可见。

删除一个xSignal

在面板中选中xSignal,然后单击xSignal列表下方的Delete按钮。或者,在上下文菜单中右键单击并选择Delete,或在键盘上按下Delete键。

xSignal查询关键词

PCB编辑器包括一个功能强大且技术精良的过滤引擎。该引擎用于在设计空间中搜索对象时进行对象识别,在交互式和自动设计任务中应用规则,以及检查规则的符合性。设计者通过使用过滤引擎识别的查询关键字编写查询,以告知过滤引擎他们对哪些对象感兴趣。

下列xSignal类型的查询关键词已被添加到设计规则和设计空间过滤器中:

成员检查类型关键词

InxSignal - 是指指定xSignal中的对象,例如,InxSignal('DRAM_A0_PP1')

InxSignalClass - 是指指定xSignal类中的对象,例如,InxSignalClass('PCIE')

IsxSignal - 是指指定名称xSignal中的对象,例如,IsxSignal('DRAM_A0_PP1')

属性检查类型关键词

InAnyxSignal - 是指任何xSignal中对象,例如,InAnyxSignal

xSignals的设计规则支持

设计规则旨在阐述如何将设计要求转化为PCB编辑器可以理解和遵守的一组指令。设计规则既可在对象放置过程中进行检查(即,Online DRC),亦可以作为一个后处理过程(即,Batch DRC)。

Matched Length 规则

Matched Length设计规则用于确保指定网络的长度在指定范围内。此规则在高速设计中至关重要,其中的挑战不仅在于信号到达需要多长时间(由其总长度决定),还在于指定信号在相同时间内到达的重要性。根据信号切换速度、信号功能以及电路板上使用的材料,允许差异既可能高达500密尔,亦可能低至1密尔。

下图所示为一个Matched Length设计规则的示例,在示例中,该设计规则配置为针对xSignal类PCIE中的xSignals,并测试该xSignals类中每个差分对的长度差异。该类中每个差分对的布线长度,须确保该差分对内两个网络之间的Delay Tolerance不超过2ps。

请注意,Matched Length设计规则的约束条件要求您选择匹配所有目标网络的长度(Group Matched Lengths),或者匹配目标网络中每个差异对内的两个网络。

下图所示为在面板上选中的PCIE_TX xSignal类,以及在设计空间中选中的xSignals。

除PCIE类之外,还有针对TX和RX对定义的类。请注意,其中一个TX xSignals不符合相关匹配长度规则。##

如果您想对包含单一网络和差分对的xSignals进行长度调整,请创建以下规则:文章来源:https://www.toymoban.com/news/detail-695451.html

定义xSignals中网络与差分对之间长度匹配要求的匹配长度规则。为了配置此规则,以参考某个网络/差分对的长度对另一个网络/差分对的长度进行测试,请启用Group Matched Lengths选项。

定义对内长度匹配要求的第二条更高优先级匹配长度规则。为了配置此规则,以参考一个差分对成员的长度对另一个差分对成员的长度进行测试,请启用Within Differential Pair Length选项。

对这类xSignals长度进行调整时,最好:文章来源地址https://www.toymoban.com/news/detail-695451.html

对xSignal的网络和差分对进行布线。

使用Interactive Length Tuning命令,对单个网络进行长度调整。

使用Interactive Differential Pair Length Tuning命令,在差分对之间进行长度调整。在进行长度调整时,应将最长差分对内的最大信号长度用作Target Length,并将该差分对内的最长网络调整至该长度。

使用Interactive Length Tuning命令,参考对内其他网络,对每个差分对内的较短网络进行长度调整。

此时,您可以使用PCB Rules and Violations面板,检查对内Matched Net Length规则。为此,请在面板的Rule Classes部分选中Matched Net Lengths,然后右键单击所需的Matched Length规则,并在上下文菜单内选中Run DRC Rule <RuleName>命令。必要时,对单一网络折叠部分进行调整。

然后,使用PCB Rules and Violations面板,按照上述过程,检查差分对之间Matched Net Length规则。必要时,对差分对调线折叠部分进行调整。

到了这里,关于高速电路设计之在Altium Designer中以xSignals定义高速信号路径的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!