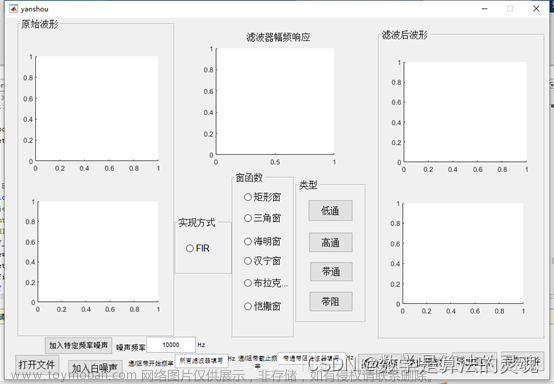

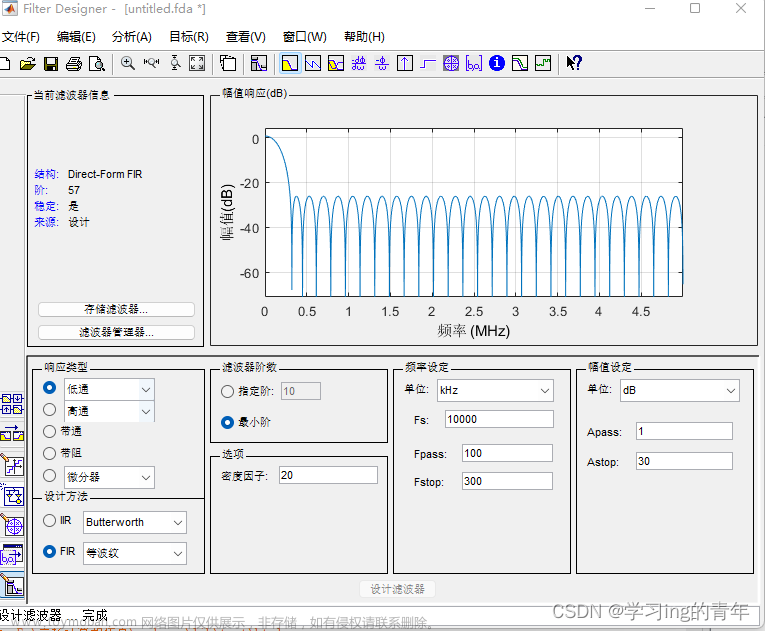

基于FPGA的FIR数字滤波器设计(quartus和vivado程序都有)。

附:

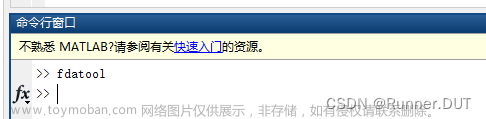

1.配套quartus从MATLAB系数生成直到仿真成功说明文档。

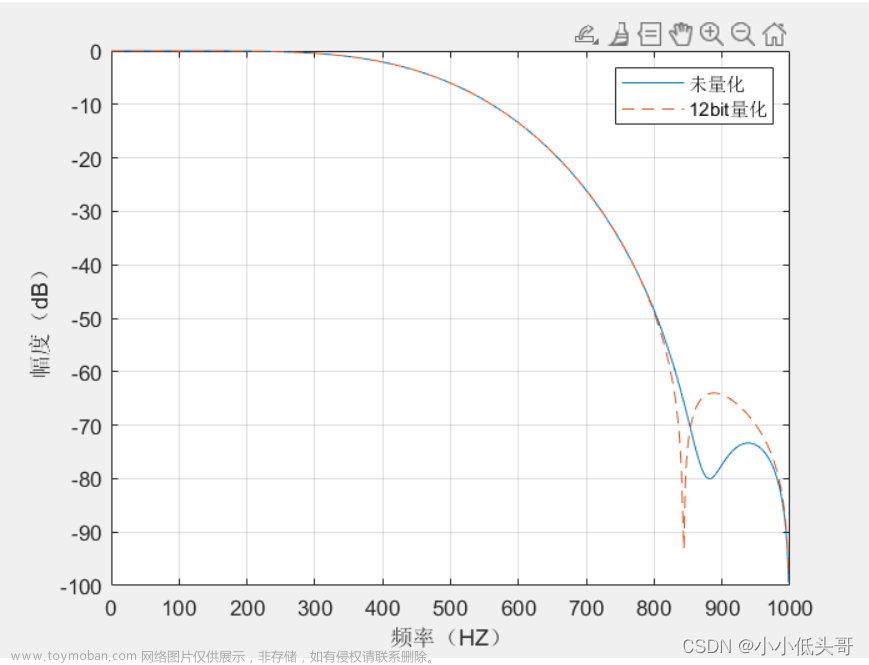

2.配套仿真出波形(图1)的视频。

文章来源地址https://www.toymoban.com/news/detail-695717.html文章来源:https://www.toymoban.com/news/detail-695717.html

到了这里,关于基于FPGA的FIR数字滤波器设计(quartus和vivado程序都有)。的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!