参考文献1

1,题目

不简单的进行移位,而是在移位的基础上加上异或门,如题目所示,这就相当于每进行一次移位,寄存器中的值会发生改变,一直移动,一直改变,就形成了伪随机数。文章来源:https://www.toymoban.com/news/detail-696947.html

2,RTL代码设计

// Verilog 实现伪随机数生成器(线性反馈移位寄存器)

module LSFR(clk, rst_n, out);

input clk;

input rst_n;

output out;

reg [4:0] shift_reg;

assign out = shift_reg[0];

always@(posedge clk or negedge rst_n)

if(!rst_n)

shift_reg <= 5'b1_1110;

else

begin

shift_reg[4] <= shift_reg[0] ^ 1'b0;

shift_reg[3] <= shift_reg[4];

shift_reg[2] <= shift_reg[3] ^ shift_reg[0];

shift_reg[1] <= shift_reg[2];

shift_reg[0] <= shift_reg[1];

end

endmodule

3,testbench测试代码

//测试

module LSFR_tb;

reg clk;

reg rst_n;

wire out;

always #10 clk = ~clk;

initial begin

rst_n = 0; clk = 1;

#15; rst_n = 1;

#123; rst_n = 0;

#233; rst_n = 1;

#500;

$stop;

end

LSFR uu(

.clk(clk),

.rst_n(rst_n),

.out(out)

);

endmodule

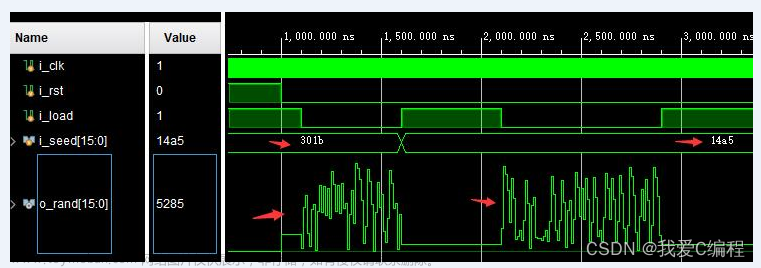

4,前仿真,波形验证

文章来源地址https://www.toymoban.com/news/detail-696947.html

文章来源地址https://www.toymoban.com/news/detail-696947.html

到了这里,关于Verilog 实现伪随机数生成器(线性反馈移位寄存器)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!