1 启动模式:

ZYNQ 7000的启动模式由外部引脚决定的,5个模式引脚MIO[6:2]用于配置NAND flash、并行NOR flash、Serial NOR (Quad-SPI)、SD flash以及JTAG 一共5种启动模式。具体而言就是复位时,zynq-7000 SOC对下述引脚进行连续3个时钟周期采样。复位采样MIO[6:2]并将采样的模式值保存到系统级控制寄存器SLCR内的BOOT_MODE寄存器内。(我们查看fsbl代码中确认当前的启动模式就是通过读取BOOT_MODE寄存器来确定不同的启动分支的)

2 关于nor flash 32M大小限制的说明:

zynq 7000的flash控制器可以配置为IO模式和线性模式,需要注意的是IO模式下才可以对flash进行读写擦操作。而线性模式下,flash相当于一个只读存储器,不能写和擦除。在IO模式下,软件负责对所有flash操作的管理;在线性模式下,控制器负责对所有必要的读数据管理。换句个人理解,系统默认的是线性模式,但是我们作为flash使用者,如果要擦写flash必须配置为IO模式,由我们自己写的驱动操作实际的flash。

注意:只有在线性模式下才有最大32M地址空间的限制,也就是说zynq 7000最大加载的fabl+bit+应用得到的boot.bin最大不能超过32M,地址映射空间就是32M。

而我们自己如果使用flash,由于使用的IO模式,实际的操作是由我们自己写的驱动管理的,和系统的内存映射没有什么关系,当然不受32M大小的限制。比如控制器可以直接连接一个128M或者两片的 norflash芯片,我们通过驱动操作flash任意地址空间(两片可以通过cs片选区分),毕竟实际操作的flash地址是我们驱动在控制和映射没关系。无非就是系统上电加载时(此时是线性模式,两片到底加载的使用的哪片flash有待研究)只能加载最大32M的底层软件而已。

3 启动流程

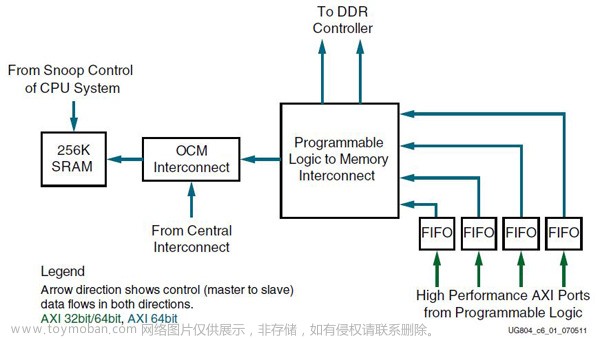

上电后在从0地址运行之前,bootRom会从nor flash(假设是nor flash启动模式)拷贝boot.bin的前n kB(小于等于192K)数据拷贝到OCM中,然后跳转到0地址OCM中开始运行。(OCM地址0000_0000 to 0003_FFFF)。随后专门写个分析boot.bin文件的内容,分析下boot.bin的数据格式

4 关于JTAG模式的说明

我们知道,ZYNQ7000支持5种启动设备,包括NAND flash、并行NOR flash、Serial NOR (Quad-SPI)、SD flash以及JTAG。我们需要知道在JTAG模式下,JTAG都是无法直接访问CPU的外设的,而是通过CPU让CPU访问外设,那么JTAG怎么知道CPU访问外设的指令呢,这是由SDK告诉的(不同芯片访问CPU的指令不同)。整个示意图如下:

SDK <-> JTAG<-> CPU <->外设

基于上面的理解,我们在回头看我们为什么需要在通过JLINK仿真器烧写boot.bin到flash时需要将FSBL代码中的读取BOOT_MODE_REG寄存器模式后改为JTAG_MODE模式,实际上我们看fsbl代码中的JTAG_MODE分支会发现并没有什么对flash的操作,那么我们烧写的操作是怎么完成的呢,正式jink通过jtag接口通知CPU访问的,并且这个时候我们也没有进行仿真模式,那么JTAG怎么知道具体什么指令呢,正是通读取SDK提供的指令表实现的。

首先执行FSBl的elf文件执行结束后进入wfe模式,然后由JTAG接管来实现对flash的更新。我们会注意到,实际上代码的作用主要就是实现JTAG模式,让后控制权交给PC机而非CPU。如果我们能更改启动模式引脚的电平,那么实际上FSBL不用更改,只需要pin改为JTAG模式即可,fsbl 文件都不需要文章来源:https://www.toymoban.com/news/detail-697314.html

5 FSBL代码可以用仿真器调试吗

fsbl代码正常是运行在OCM中的,我们看FSBL代码配置的ld文件也是OCM地址空间,所以仿真器会将elf直接加载到OCM空间,OCM和DDR都是我们应用可以访问的有效地址,当然可以直接仿真调试。文章来源地址https://www.toymoban.com/news/detail-697314.html

到了这里,关于Xilinx ZYNQ 7000学习笔记三(小结)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!